# INSTITUTO UNIVERSITARIO AERONAUTICO

# DISEÑO, SIMULACIÓN E IMPLEMENTACIÓN EN FPGA DE UN FILTRO ADAPTADO CON APLICACIÓN A CONTRA CONTRA MEDIDAS ELECTRÓNICAS.

# MALDONADO, Hugo MOLINA, Luciano

Presentado ante la facultad de Ingeniería del Instituto Universitario Aeronáutico, para la obtención del título de grado "Ingeniero en Telecomunicaciones".

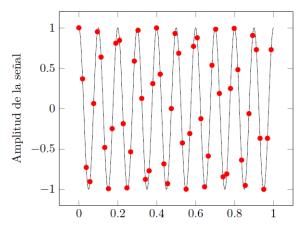

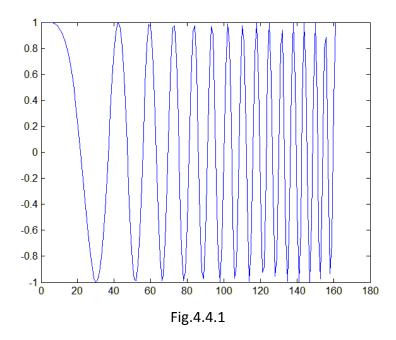

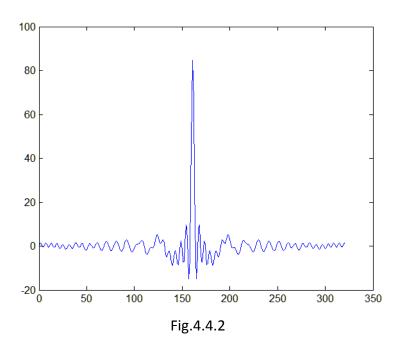

Tutores: NAGUIL, Jorge GLOZA, Gonzalo

Tribunal de Evaluación: SAUCHELLI, Víctor Hugo FERREYRA, Pablo Alejandro Diseño, Simulación e Implementación en FPGA de un Filtro Adaptado con aplicaciones a contra contra medidas electrónicas.

Instituto Universitario Aeronáutico Córdoba, Argentina. Diciembre de 2011

# RESUMEN

Frente la necesidad del grupo de trabajo encargado del Programa de Investigación y Desarrollo para la Defensa (PIDDEF), surge la propuesta de desarrollo e implementación de un algoritmo para el tratamiento de señales en tiempo real con aplicación a la Defensa Electrónica.

En los comienzos del trabajo se analizaron teóricamente los algoritmos disponibles para el tratado de señales que cumplan con los requisitos de matched filtering. Para obtener resultados prácticos se realizaron un serie de pruebas y simulaciones en MatLab® que permitieron determinar si el algoritmo en cuestión se adapta a los objetivos del proyecto. Particularmente se realizó el estudio de pre-factibilidad del algoritmo LMS y se analizó las posibilidades reales de ser aplicado a un sistema RADAR. Por otro lado se desarrolló el modelo basado en la teoría del filtro apareado con el cual se obtuvieron mejoras acordes a las metas establecidas en los objetivos específicos del trabajo.

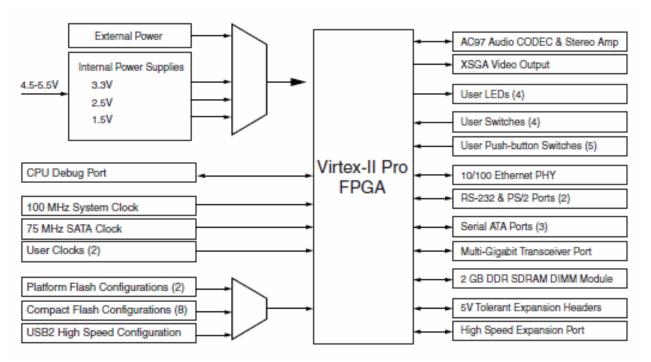

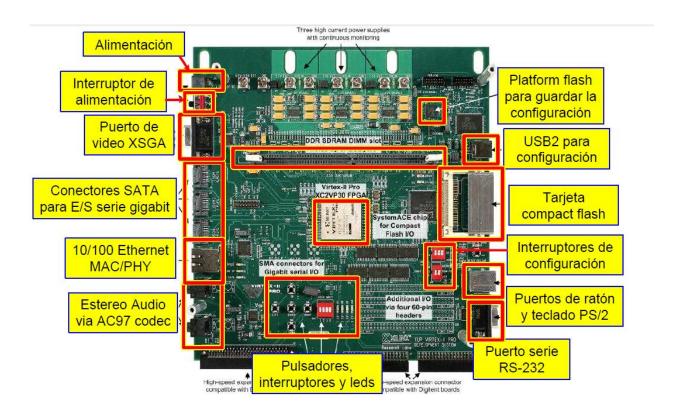

Como segunda etapa de desarrollo se reunió información de los métodos de implementación sobre plataforma digital. Se estudiaron las placas que actualmente se encuentran a nuestra disposición determinando, según sus correspondientes hojas de especificaciones, aquella que contenga el hardware necesario para lograr los tiempos de procesamiento adecuados al sistema que se implementará en ella. Se concluyó que la plataforma Xilinx® Virtex-II es de utilidad para el trabajo.

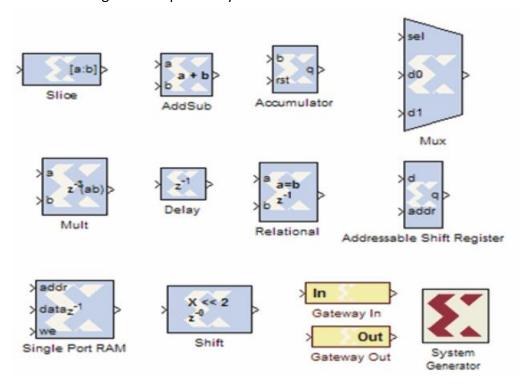

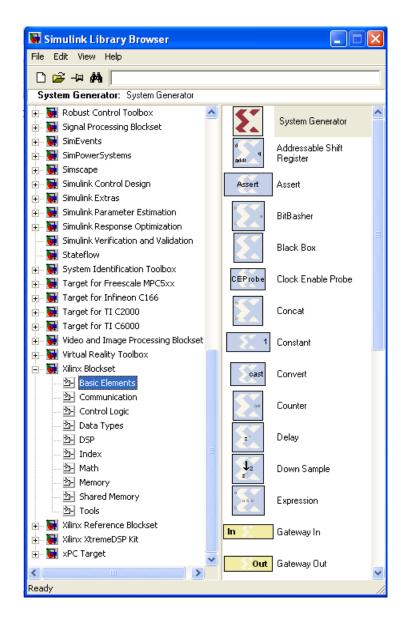

Por último se utilizaron herramientas de software para la práctica de hardware in the loop. Particularmente System Generador, como aplicación de MatLab®, provee la lógica necesaria para la implementación física del modelo desarrollado. Se contrastaron los resultados simulados y los obtenidos de la implementación para el análisis de resultados, los cuales fueron expuestos al final de este informe.

# ÍNDICE GENERAL

| INTROD  | UCCIÓN GENERAL                                                  | 15 - |

|---------|-----------------------------------------------------------------|------|

| OBJETIV | O DEL PROYECTO                                                  | 17 - |

| CAPÍTU  | JLO 1: LA GUERRA DE INFORMACIÓN                                 |      |

| 1.1     | INTRODUCCIÓN                                                    | 18 - |

| 1.2     | PILARES DE LA GUERRA DE INFORMACIÓN                             | 18 - |

| 1.3     | LA GUERRA ELECTRÓNICA                                           | 19 - |

| CAPÍTU  | JLO 2: EL RADAR                                                 |      |

| 2.1     | INTRODUCCIÓN                                                    | 20 - |

| 2.2     | EVOLUCIÓN NACIONAL DEL RADAR                                    | 20 - |

| 2.3     | PRINCIPIO DE FUNCIONAMIENTO                                     | 22 - |

| 2.4     | ECUACIÓN BÁSICA DEL RADAR                                       | 24 - |

| 2.5     | FUENTES DE RUIDO INEVITABLES                                    |      |

| 2.6     | RUIDO INTENCIONAL – CONTRAMEDIDAS ELECTRÓNICAS                  | 27 - |

| 2.7     | RUIDOS PROPIOS DEL RECEPTOR                                     | 28 - |

| 2.8     | PROBABILIDAD DE DETECCION, PROBABILIDAD DE FALSA ALARMA Y       |      |

| RELA    | CIÓN SEÑAL A RUIDO                                              | 30 - |

| 2.9     | TIPO DE SEÑALES DE RADAR                                        | 34 - |

| 2.10    | COMPRESIÓN DE PULSOS                                            | 35 - |

| 2.11    | COMPRESION DE PULSO LFM                                         | 36 - |

| 2.12    | MODELO DE TRANSMISOR                                            | 38 - |

| 2.13    | TECNICAS DE VENTANEO                                            | 39 - |

| 2.14    | EL RECEPTOR RADAR                                               | 40 - |

| CAPÍTU  | JLO 3: PROCESAMIENTO DIGITAL                                    |      |

| 3.1     | INTRODUCCIÓN                                                    | 42 - |

| 3.2     | FILTROS DIGITALES                                               | 42 - |

| 3.3     | FILTROS FIR                                                     | 45 - |

| 3.4     | PLATAFORMAS DIGITALES                                           | 52 - |

| 3.5     | INTRODUCCIÓN A LAS FPGA. XILINX VIRTEX II PRO Y PLACA DE DESARR | OLLO |

| XUPV    | 2P                                                              | 53 - |

| 3.6     | HERRAMIENTAS DE DISEÑO.                                         | 58 - |

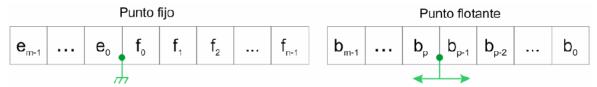

| 3.7     | ARITMETICA DE PUNTO FIJO Y CUANTIFICACIÓN.                      | 66 - |

| CAPÍTU  | JLO 4: MATCHED FILTER                                           |      |

| 4.1     | INTRODUCCIÓN                                                    | 74 - |

| 4.2     | DESARROLLO TEÓRICO                                              |      |

| 4.3     | OBTENCIÓN DE LA RESPUESTA EN FRECUENCIA DEL MATCHED FILTER      |      |

| 4.4     | SIMULACION DEL MATCHED FILTER EN MATLAB                         |      |

| 4.5   | DISEÑO Y SIMULACIÓN DEL MATCHED FILTER EN MA        | TLAB/SIMULINK 82 - |

|-------|-----------------------------------------------------|--------------------|

| CAPÍT | TULO 5: IMPLEMENTACIÓN                              |                    |

| 5.1   | INTRODUCCIÓN                                        |                    |

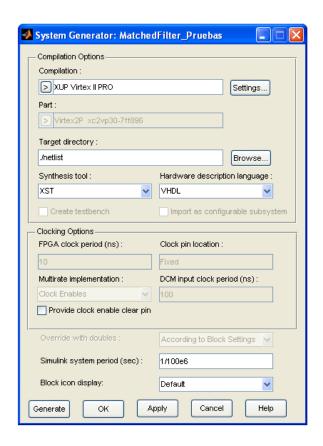

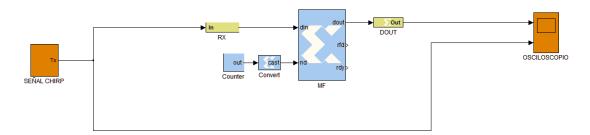

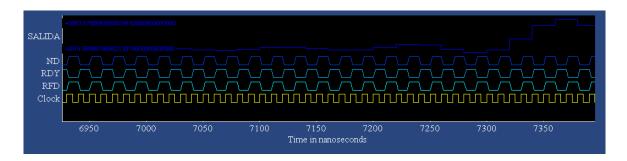

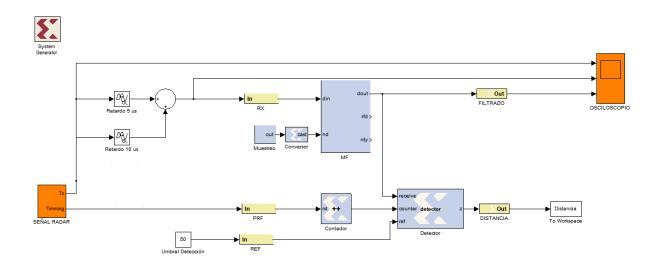

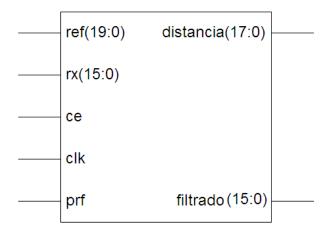

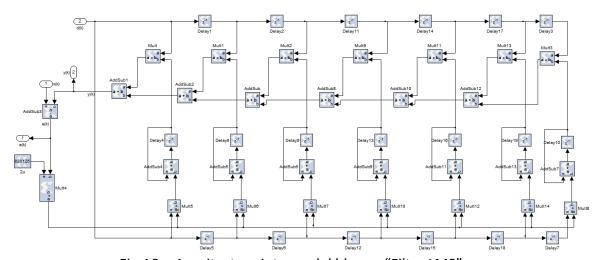

| 5.2   | DISEÑO EN SYSTEM GENERATOR                          | 88 -               |

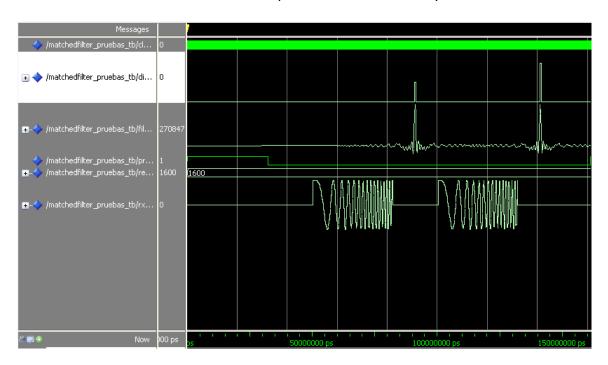

| 5.3   | SIMULACION HDL                                      | 92 -               |

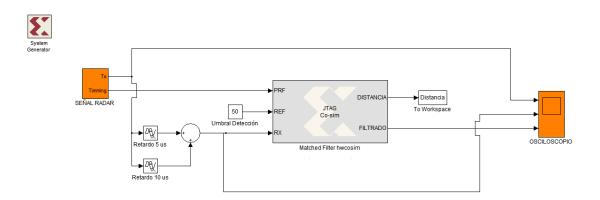

| 5.4   | COSIMULACION POR HARDWARE                           | 92 -               |

| DESAF | TULO 6: RESULTADOS, CONCLUSIONES Y PROPU<br>RROLLOS |                    |

| 6.1   | INTRODUCCIÓN                                        |                    |

| 6.2   | RESULTADOS                                          |                    |

| 6.3   | CONCLUSIONES                                        |                    |

| 6.4   | DESARROLLOS FUTUROS                                 | 101 -              |

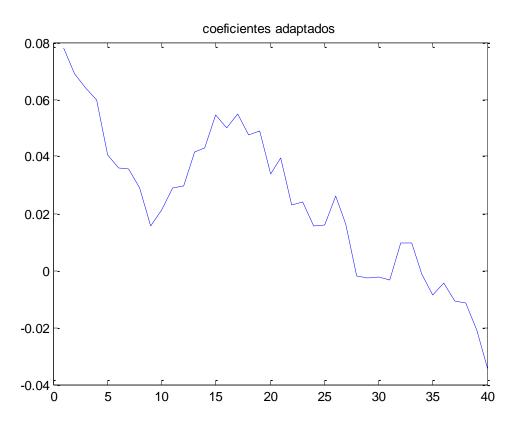

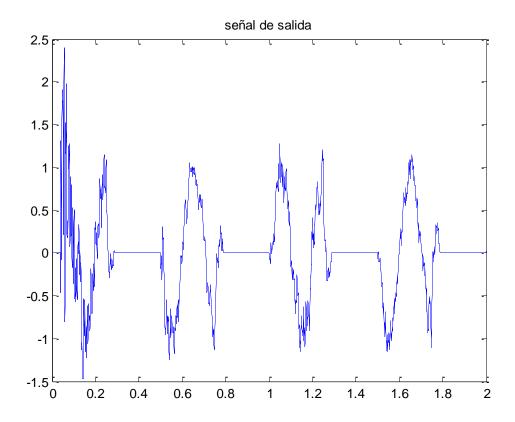

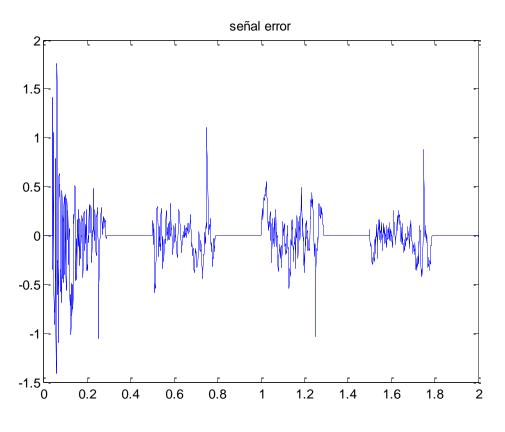

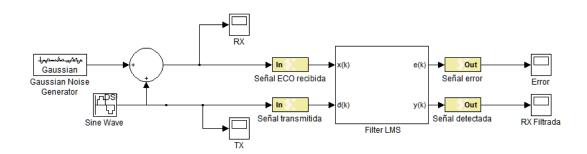

| ANEX  | O A: FILTRO ADAPTIVO LMS                            | 103 -              |

| FILTE | RO ADAPTIVO – LMS EN SIMULINK                       | 109 -              |

| REFER | RENCIAS                                             |                    |

# INTRODUCCIÓN GENERAL

El procesamiento de señales ha ocupado un lugar de privilegio dentro de cualquier tipo de sistema electrónico, aprovechando la miniaturización y el incremento de la capacidad de los elementos para el desarrollo de tecnologías funcionales en distintos campos de aplicación.

La invención del radar proporcionó una herramienta muy útil principalmente con fines militares, proveyendo a las fuerzas de un arma con gran poder táctico y de protección. Surge como actividad derivada de la incorporación de este nuevo instrumento, aquellos estudios de las señales que utiliza para prever como podría el enemigo alterar, dañar, o eludir las señales emitidas por el radar, y de esta manera acomplejar el equipamiento propio dificultándole la tarea al adversario.

Saber cuándo el enemigo envía flotas, aviones, o detectar proyectiles a gran distancia puede resultar una actividad vital en el transcurso de un pleito entre naciones. Por lo que mientras más seguro, confiable, preciso y menos vulnerable sea el instrumento que detecte estas amenazas, mayor ventaja se tendrá sobre el enemigo.

La no vulnerabilidad del equipo se logra luego del estudio de los métodos que se utilizan para interferir el buen funcionamiento de él. Generalmente estos intentos se realizan con fuentes interferentes que atentan contra la señal de interés añadiéndole una gran cantidad de ruido.

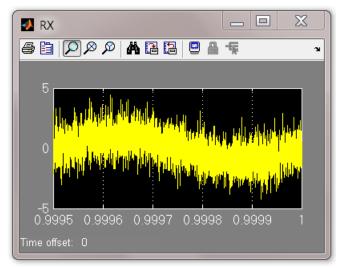

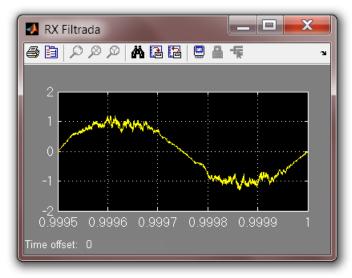

En este sentido la finalidad del presente Trabajo Final de Grado es el estudio, desarrollo e implementación en FPGA de un filtro apareado, aplicado a contra contra medidas electrónicas. Él mismo fue diseñado para evitar que la interferencia destruya completamente la información, optimizando el funcionamiento del receptor mediante la maximización de la relación señal a ruido a la salida de éste.

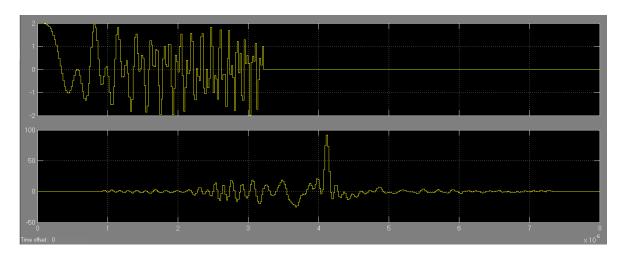

Al ser el alcance de este proyecto diseñar un filtro aplicado a radar y debido a la falta de instrumentación de laboratorio especializada para sistemas de radio, como generadores e interfaces de señal de radar aptos para este proyecto, analizadores lógicos, y componentes como Conversores Analógicos-Digital (ADC por sus siglas en ingles de Analog to Digital Converter) y Digital-Analogico (DAC por sus siglas en ingles de Digital to Analog Converter), solo se realizó la comprobación de su correcto funcionamiento mediante simulaciones tanto a nivel sistema como a nivel funcional en lenguaje de descripción de hardware. Además se introduce un tipo de simulación adicional de mayor precisión denominada co-simulación por hardware, donde el diseño es implementado en la FPGA, posibilitando la utilización de un software de computadoras para trabajar como si fueran generadores de señales y analizadores lógicos y de espectro. Estos procesos permiten determinar si el diseño es factible de implementar en la plataforma seleccionada.

El informe comienza con la descripción de la Guerra Informática con el objeto de acotar el campo de aplicación del radar orientando el trabajo al uso militar del mismo. En el capítulo 1 se desarrollan los métodos utilizados en la Guerra Electrónica para la práctica de las ECM (contra medidas electrónicas) y las ECCM (contra contra medidas electrónicas).

El capítulo 2 presenta al sistema radar. Se desarrolla la teoría básica de funcionamiento, las fuentes de ruido con las que interacciona y los modelos utilizados como trasmisor y receptor.

El capítulo 4 describe el procesamiento digital, donde se incluyen los tipos de filtros posibles de utilizar, haciendo hincapié y profundizando el estudio en el filtro FIR que fue el seleccionado para este trabajo. Se incluyen las plataformas digitales presentes en el mercado en particular la Virtex II usada para la implementación del Matched Filter. Al final del capítulo 3 se analizan las herramientas de software utilizadas para la simulación, co-simulacion e implementación del filtro y los errores de cuantificación generados al digitalizar una señal.

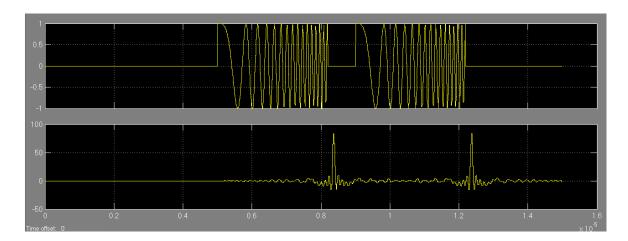

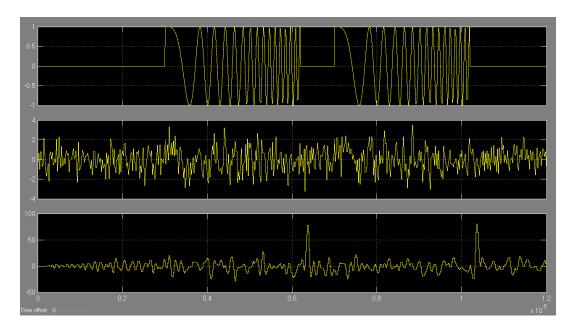

El capítulo 4 desarrolla el Matched Filter, se estudia su teoría y se muestran las simulaciones realizadas tanto en MatLab como en Simulink.

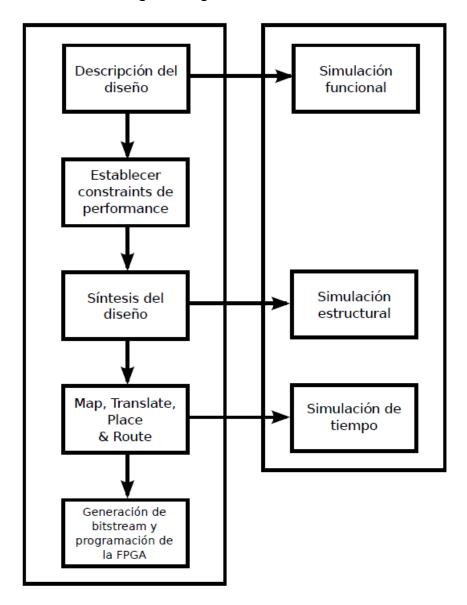

La implementación física del modelo se realiza en el capítulo 5, respetando los pasos necesarios para optimizar el proceso completo de implementación. Se muestra paso a paso las distintas etapas por las que se debe pasar antes de la programación final de la placa.

En el capítulo 6 se analizan los resultados obtenidos, llegando a conclusiones respecto al rendimiento del filtro. También se realizan propuestas para continuar con el desarrollo del filtro y modelos de receptor con un mayor grado de calidad en función a requerimientos de las ECCM.

# **OBJETIVO DEL PROYECTO.**

Una vez implementado el filtro apareado se corroboró su verdadera necesidad dentro de un sistema de radar. Con los resultados obtenidos y mediciones tomadas se realizaron objeciones que determinen si la incorporación del mismo en el procesamiento de señales de radar es de utilidad, primordial, o por el contrario puede prescindirse de él.

Para ello se consideraron los siguientes objetivos específicos:

- Análisis de las señales RADAR, y su interacción con el medio.

- Diseño del Matched Filter.

- Simulación del filtro diseñado.

- Selección de la arquitectura a implementar.

- Dimensionamiento de la plataforma de implementación.

- Implementación del sistema sobre plataforma digital.

- Verificación y validación.

- Conclusiones y Observaciones.

El beneficiario directo de este trabajo es el grupo encargado del proyecto PIDDEF, el cual tiene a su cargo el estudio de métodos y sistemas en el campo de la Guerra Electrónica.

# **CAPÍTULO 1: LA GUERRA DE INFORMACIÓN**

# 1.1 INTRODUCCIÓN

En todo sistema de comunicación es importante mantener seguro los datos que se trasmitan. Este problema se acentúa cuando esos datos se trasmiten por el aire y llevan información que puede ser utilizada por el enemigo para determinar, por ejemplo, nuestra posición. La acción de proteger los datos y la de intentar obtener información del enemigo se conoce como guerra informática. La protección de la información no es tarea de los últimos tiempos, el continuo desarrollo y el incremento en la necesidad de protección influyen en el estudio de nuevos métodos aplicables a la defensa y al ataque.

Este tipo de guerra no solamente está aplicado al uso militar, sino también en todo aquel sistema que requiera de un alto grado de seguridad para su información. Las grandes compañías manejan información totalmente confidencial, cuya divulgación o intercepción por parte de la competencia podría influir considerablemente en el futuro, e incluso culminar con la existencia de ella.

# 1.2 PILARES DE LA GUERRA DE INFORMACIÓN

Los procedimientos a realizarse luego de la obtención de información del medio de propagación compartido por los agentes en conflicto, pueden estar dentro de los siguientes puntos generales [1]:

- Destrucción de los sistemas de información.

- Operaciones psicológicas.

- El engaño.

- Operativos de seguridad.

- Guerra Electrónica.

La destrucción de los sistemas de información sería el caso extremo, cuando la hostilidad ya se encuentra en marcha. Las operaciones psicológicas son usadas hace varios años. Hacer creer sobre una situación que no está sucediendo, por ejemplo, trasmisiones de radio en una región para aparentar un fuerte armamento, pueden ser tácticas muy efectivas.

Procedimientos para cuidar información útil para el enemigo, como utilizar contenedores, o mantener precauciones durante una llamada telefónica, puede ser determinante en una IW (Guerra Informática), éstos son ejemplos de Operativos de Seguridad.

La guerra electrónica es la actividad que tiene como objetivo explotar, reducir o impedir el uso de parte o la totalidad del espectro electromagnético, para obtener algún tipo de beneficio propio. Es éste el ámbito donde se desarrollan las actividades de ECM (Contra Medidas Electrónicas), y ECCM (Contra Contra Medidas

Electrónicas). Particularmente el filtro adaptado se encuentra dentro de los procedimientos de ECCM.

# 1.3 LA GUERRA ELECTRÓNICA

Todo equipo militar tiene a su disposición distintos sistemas que intentan lograr una posición estratégicamente superior a la del adversario, mediante el aprovisionamiento de datos. Estos datos pueden interpretarse para obtener información sobre posicionamiento, tipos de suelo, detección de blancos, velocidad de blancos, entre otros. Pero a su vez, el "atacante", puede interferir en la obtención de estos datos, al utilizar el mismo espacio radioeléctrico, y de esta forma atenuar, evitar o modificar los datos que intentamos descifrar. Estas prácticas comenzaron en la segunda guerra mundial, junto con la invención del radar, y no han parado hasta el momento, más aún, se ha convertido en uno de

del radar, y no han parado hasta el momento, más aún, se ha convertido en uno de los factores determinantes en la valoración de supervivencia y vulnerabilidad. Básicamente la guerra electrónica consta de tres actividades [1].

- Soporte electrónico: Adquirir información del adversario interceptando su energía irradiada. Dentro del espacio de frecuencias en que trabaja un equipo se encuentran numerosas fuentes de interferencia, unas inevitables y otras no, por lo que hay que detectar cuál de esas fuentes forman parte de un ataque electrónico. Puede reunirse información útil con solo medir parámetros externos, como frecuencia, modulación, tasa de transmisión, etc. Luego "inteligencia de señales" se encarga de obtener más información.

- Ataque electrónico: Transmisión de señales para evitar el acceso enemigo a la información. Recordamos que la señal que quiere acceder a nuestra información puede provenir de diferentes sistemas, por lo que se deben conocer parámetros básicos para poder interferirla. Ej.: jamming (ver sección 2.9).

- Protección Electrónica: Consiste en el uso de estrategias para evitar las dos primeras actividades. El conocimiento del espacio en el que se va a tratar de transmitir la señal es cada vez más importante en la era de la guerra de información, para lograr que se trasmita de manera precisa, y oportuna. De igual forma se debe cuidar la información que se trasmite y que no sea manipulable por el enemigo. Se puede realizar la protección electrónica de muchas maneras. EMCON (Control de emisiones) es una de las más simples, en la que solo se permite trasmitir en determinados períodos de tiempo, haciendo dificultoso para el enemigo interceptar e identificar la frecuencia de trabajo. Otra manera de proveer protección es con el uso de baja probabilidad de detección de la comunicación (spread spectrum, ver el capítulo 3). Screen Jamming es otra herramienta para proteger información, colocando un jammer entre la red de comunicación y el sistema enemigo, para evitar que este último acceda a la información. También se puede realizar la encriptación de la información.

# CAPÍTULO 2: EL RADAR

# 2.1 INTRODUCCIÓN

La palabra RADAR es la abreviatura de Radio Detection And Ranging, básicamente su funcionamiento se basa en la transmisión de energía electromagnética en un determinado espacio, por medio de ondas moduladas, con el propósito de detectar diferentes clases de objetivos. La detección se logra cuando las ondas trasmitidas impactan sobre la superficie de los objetivos que se encuentran dentro del espacio cubierto por el radar y producen reflexiones que regresan hacia él. El receptor se vale de estos ecos para determinar el rango, velocidad, posición angular y demás información sobre el objetivo que produjo su respectivo eco.

Puede clasificarse los radares según su campo de aplicación. Por ejemplo, radares militares, aeronáuticos, marítimo, meteorológico, circulación y seguridad, etc.

Otra clasificación es según la forma de onda que transmita, por ejemplo, onda continua, continua con modulación o del tipo pulsado. Este último es aquel que utiliza como señal trasmitida un tren de pulsos que modula una señal sinusoidal, y pueden identificarse tres tipos, los de baja frecuencia, media frecuencia, y alta frecuencia que utilizan la ionosfera para detectar objetos más allá del horizonte visual. De aquí en adelante trataremos con radares pulsados.

Según el modo de funcionamiento se distinguen el radar primario y el radar secundario. El primario detecta la presencia de un blanco basándose en la energía reflejada. El secundario es un radar activo que envía una serie de pulsos a la aeronave. El transpondedor responde con su identificación, velocidad, rumbo y demás datos de importancia.

El filtro que se desarrolla en este trabajo se aplica a radar primario cumpliendo con los requerimientos del Proyecto PIDDEF.

# 2.2 EVOLUCIÓN NACIONAL DEL RADAR

En 1947 se dejó en manos de la recién creada Aeronáutica Militar el poder de ejercer la autoridad aeronáutica para la gestión del tránsito aéreo civil. Frente a un crecimiento, tanto de la aviación comercial como de la aviación general, a fines de la década del 70 y comienzos del 80 la fuerza aérea encaro un proyecto de control del espacio aéreo, con doble función, el apoyo a la aviación civil y el apoyo a la defensa aeroespacial, denominado Sistema Integrado de Control del Espacio Aéreo (SICEA).

Este proyecto comenzó con la instalación de un sistema de control en las cercanías del aeropuerto de Ezeiza, pero debido a su costo insostenible tuvo que ser dejado de lado apenas finalizado la cuarta parte de él.

Mientras tanto, en 1987 la Fuerza Aérea realizó la primera actualización y puesta a cero de un Radar Thomson instalado en 1973 para el área terminal de Buenos Aires junto con el centro de control de Ezeiza.

La próxima incorporación se realizó en el año 1986 en la ciudad de Córdoba, instalando un radar y centro de control, adquiridos en la empresa italiana "Alenia":

En 1992, la fuerza aérea encara un nuevo proyecto de control aéreo civil con la idea de ser financiado por los propios fondos de la fuerza, que luego de su gestión y posterior aprobación concluyo como el Plan Nacional de Radarización. Teniendo en cuenta que el costo del proyecto rondó los 400.000 millones de dólares, la misma ley que habilitó el plan, permitió al Ministerio de Defensa realizar una licitación internacional para una primera etapa del plan nacional de Radarización.

Mientras se implementaba dicho plan, en 1994 la fuerza aérea inaugura la infraestructura de un sitio Radar y centro de control en Mendoza, en este caso donado por el gobierno italiano.

En 1995 se actualizó el radar secundario del sitio de Ezeiza, convirtiéndolo en uno de última generación con la característica de ser Monopulso.

En 1996 se instala un Radar secundario monopulso con el fin de proveer información al radar de Córdoba y Ezeiza respecto al movimiento en ruta aérea de las aeronaves.

En 1997 se instala un Radar y Centro de control en el área Terminal de mar del Plata. En este mismo año la OACI habilitó los Radares monopulso para brindar servicio de aproximación de aeródromos, lo que llego a una tercera actualización del radar de Ezeiza, permitiéndole girar a 7,5 RPM. También se encara la puesta a cero de los Radares de Córdoba y Mendoza.

A fines del año 1997 se produce la apertura de las ofertas Técnicas del Plan Nacional de Radarización. En el año 1999, ya adjudicada la concesión, debió ser anulada debido a denuncias realizadas por la empresa perdedora de dicha licitación. Demoras que llevan a un nuevo plan de Radarización en el año 2001.

Se tuvo que tener en cuenta el error informático llamado "Y2K", deficiencias de los software's al pasar a un nuevo milenio. Esto llevo a una pequeña actualización del Radar de Ezeiza.

Mientras se decidía sobre el nuevo plan nacional, las necesidades técnicas no podían dejarse de lado, por lo que con el apoyo extra-presupuestario del Ministerio de Defensa, la Fuerza Aérea encara la total actualización del radar de Ezeiza. Actualización que no solo brinda información Radar, sino que realizaba el tratamiento automático de planes de vuelo y apoyo a la toma de decisiones en el control de flujo aéreo. Dado que este Radar se convirtió en el Centro de Gestión de Tráfico Aéreo, no solo procesaba la información proporcionada por el mismo, sino también la información proporcionada por los Radares de Mendoza, Mar del Plata, Paraná y Córdoba, y de acuerdo con la Administración de Aviación Civil de Uruguay, el Radar Carrasco.

A partir del año 2002 la fuerza aérea investiga junto con INVAP la posibilidad del desarrollo de Radares Secundarios Monopulso de última generación. Estudio que luego fue aprobado por el Ministerio de Defensa y autoridades Nacionales, posibilitando la fabricación no solo del prototipo sino también de diez radares más disponibles para la gestión de tránsito aéreo civil.

En 2003 la empresa nacional INVAP ya tenía a su cargo la tarea de mejoramiento de los servicios de control de tráfico, proporcionando un control unificado de todas las áreas terminales y aerovías del país.

En el año 2004 quedó establecido el Sistema Nacional de Vigilancia y Control Aeroespacial (SINVICA) cuyo objetivo es el control efectivo del espacio aéreo nacional para la aviación civil y la defensa. Como objetivo secundario (y muy

importante) fue dar la mayor participación de la industria argentina para su implementación.

Así nació, a cargo de INVAP, el Plan Argentino de Desarrollo de Sensores Radar. Plan que permitió la instalación del primer radar argentino 3D operativo en el corriente año, y hasta el momento 8 radares secundarios funcionando en los aeropuertos de Quilmas, Santa Rosa, Neuquén, Bariloche, Bahía Blanca, Córdoba, San Luis y Tucumán.

## 2.3 PRINCIPIO DE FUNCIONAMIENTO

Uno de los principales propósitos del radar primario es detectar un objeto y determinar la distancia a la cual se encuentra. Esta distancia se denomina rango y se obtiene a partir del tiempo en que tarda un pulso en ir hasta el objeto y regresar de él. Matemáticamente, el rango está dado por:

$$R = \frac{c.\Delta t}{2}$$

; R[m],  $\Delta t$ [s], c[m/s] Ec.2.3.1

Dónde:

R = Rango o distancia a la que se encuentra el blanco.

$c = \text{Velocidad de la luz } (3x10^8 \text{ m/s}).$

$\Delta t$  = Tiempo de retardo del eco procedente del blanco detectado.

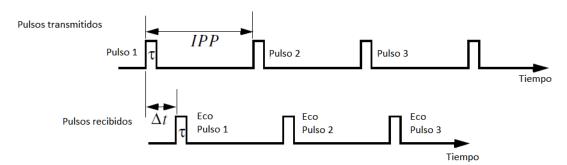

En la figura 2.3.1 se muestran los pulsos trasmitidos y los ecos que llegan al receptor luego de ser reflejados por el objetivo. En este caso se suponen pulsos ideales sin interferencias ni atenuaciones, alteraciones que en la práctica son inevitables.

Fig. 2.3.1 - Pulsos transmitidos y ecos recibidos.

A partir de la figura anterior podemos establecer los siguientes parámetros.

Período de repetición del Pulso:

$$IPP = T = \frac{1}{fr}$$

Ec.2.3.2

Donde fr es la frecuencia de repetición de pulsos.

El ancho de banda del pulso está dado por:

$$B = \frac{1}{\tau}$$

Ec.2.3.3

Donde  $\tau[s]$  es la duración del pulso.

En cada período sólo se trasmite energía durante  $\tau$  segundos, el resto del tiempo se espera el eco. Se define como Ciclo de Trabajo a la relación entre el período de repetición de pulsos y el ancho del pulso (Ecuación 2.3.4).

$$d_{t} = \frac{T}{\tau}$$

Ec.2.3.4

La potencia promedio trasmitida es,

$$P_{av} = P_t \cdot d_t$$

Ec.2.3.5

Donde  $P_t$  es la Potencia pico transmitida.

La energía del pulso es,

$$E = P_t \cdot \tau = P_{av} \cdot T = \frac{P_{av}}{f_r}$$

Ec.2.3.6

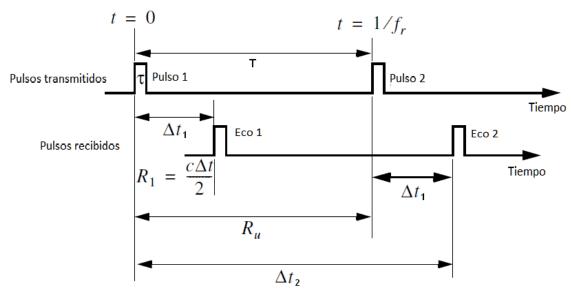

Al trasmitir dos pulsos consecutivos, el segundo eco recibido puede ser interpretado de dos maneras distintas. La primera alternativa es considerarlo como un segundo eco producido por el mismo objetivo que produjo el primer eco. La segunda alternativa es considerarlo como un eco del primer pulso, producido por un objetivo muy alejado. Estos casos se representan como sigue,

$$R_2 = \frac{c.\Delta t_2}{2}$$

ó  $R_2 = \frac{c.(T + \Delta t_1)}{2}$  Ec.2.3.7

Dónde:

$R_2$  = Rango o distancia a la que se encuentra el segundo blanco.

$\Delta t_2$  = Tiempo de retardo del eco procedente del posible segundo blanco detectado.

$\Delta t_1$  = Tiempo de retardo del eco procedente del primer blanco detectado.

Este análisis puede observarse en la figura 2.3.2 a continuación.

Fig. 2.3.2 – Análisis e interpretación de los ecos recibidos.

El rango inequívoco es asociado el rango 2 debido a la incertidumbre que ocasiona. Entonces, una vez que el radar trasmite el primer pulso debe esperar lo suficiente como para que el eco producido por el objetivo más alejado regrese antes que se trasmita el segundo pulso. El valor de esta espera se conoce como Rango Inequívoco y se calcula como sigue:

$$R_u = \frac{c.T}{2} = \frac{c}{2.f_r}$$

Ec.2.3.8

# 2.4 ECUACIÓN BÁSICA DEL RADAR

Si la potencia Pt es trasmitida por una antena isotrópica, la densidad de potencia a una distancia R del radar es,

$$P_D = \frac{P_t}{4\pi R^2}$$

Ec.2.4.1

Dónde P<sub>D</sub> es la Densidad de Potencia

Al utilizar una antena que presenta ganancia en una determinada dirección (Directividad), respecto a la antena isotrópica, la ecuación 2.4.1 se modifica como sigue:

$$A_{ef} = \frac{G.\lambda^2}{4\pi}$$

Ec.2.4.2

Dónde:

$A_{ef}$  = Área efectiva de la antena.

G = Ganancia de la antena.

$\lambda$  = Longitud de onda de la frecuencia de señal transmitida.

$$P_D = \frac{P_t \cdot G_{tx}}{4\pi R^2}$$

Ec.2.4.3

Cuando la energía radiada por la antena trasmisora incide en un objeto este refleja ondas en todas direcciones. La cantidad de energía reflejada es proporcional al tamaño del objeto, orientación, forma, tipo de material, etc. Todo estos factores se incluyen en un parámetro denominado RCS (Radar Cross Section de sus siglas en inglés) y se identifica con  $\sigma$ .

$$\sigma = \frac{P_r}{P_D}$$

Ec.2.4.4

Dónde  $P_r$  es la potencia reflejada por el blanco.

Por lo tanto la densidad de potencia recibida por el radar es:

$$P_{Dr} = \frac{P_t \cdot G_{tx} \cdot \sigma \cdot A_{ef}}{\left( (4\pi R)^2 \right)^2}$$

Ec.2.4.5

A partir de la ecuación 2.4.2 se puede definir entonces que:

$$P_{Dr} = \frac{P_t \cdot G^2_{tx} \cdot \sigma \cdot \lambda^2}{(4\pi)^3 \cdot R^4}$$

Ec.2.4.6

Para obtener el rango máximo posible, se utiliza la sensibilidad del receptor  $S_{\min}$  . Luego:

$$R_{\text{max}} = \left(\frac{P_{t}.G_{tx}^{2}.\sigma.\lambda^{2}}{(4\pi)^{3}.S_{\text{min}}}\right)^{1/4}$$

Ec.2.4.7

# 2.5 FUENTES DE RUIDO INEVITABLES

La señal trasmitida incide sobre la superficie reflectora, y el receptor capta esta pequeña porción de señal. El nivel de la señal recibida debe superar un valor umbral y el nivel de relación señal a ruido preestablecidos por el fabricante del receptor. Se interpreta como ruido a toda energía electromagnética que atenta contra la habilidad del receptor para detectar la energía deseada.

En la práctica el nivel de ruido es el factor decisivo al momento de establecer si la señal es legible o no. Si bien la intensidad de señal es un parámetro importante, en realidad el parámetro de nuestro interés y determinante en la detección de un blanco es la relación señal a ruido.

Existen diversas fuentes de ruido, a continuación se mencionan alguna de ellas:

# Ruido térmico:

Se debe al movimiento de los electrones por el solo hecho de estar por encima del cero absoluto. Puede ser trasladada o irradiada como cualquier otro tipo de energía electromagnética. En el dominio del tiempo el ruido térmico presenta una distribución gaussiana. Constante para todo el rango de frecuencias.

# Fuentes de ruido internas:

Es causado por el choque de los electrones dentro de los conductores. Esos choques se deben al movimiento aleatorio que presentan los electrones. La corriente eléctrica puede considerarse como un control en la dirección de ese movimiento aleatorio. Todo componente en la práctica presenta una resistencia, lo que causa la existencia de este tipo de ruido.

Cada circuito del receptor genera ruido térmico, y gran parte de éstos se suman a la señal. Todas estas fuentes de ruido están referidas a la entrada del receptor. Puede referirse todas estas fuentes de ruido a la entrada del receptor, incluyéndolas en un parámetro denominado figura de ruido (F), y luego considerar a ese receptor libre de ruido. Este ruido puede incluirse en el ruido total equivalente

N=K.T.B.F Ec.2.5.1

## Dónde:

N = Ruido Térmico.

$K = Constante de Boltzmann, 1.381 \times 10^{-23} J K^{-1}$ .

B = Ancho de Banda de Trabajo.

F = Figura de Ruido.

La interferencia y compatibilidad electromagnética puede suceder debido a los osciladores y a los clock`s del sistema.

#### Fuentes de Ruido Externas:

Existen diversas fuentes de ruido externas al sistema, que varían según el rango de frecuencias que se considere. Muchas maquinas creadas por el hombre producen interferencias, por ejemplo, máquinas de soldadura, el arranque de un auto o el horno microondas. La cantidad de este tipo de ruido presente, depende del número de fuentes interferentes, por lo tanto, el ruido es mayor en regiones densamente pobladas que en zonas rurales.

La atmósfera que rodea la tierra contiene energía térmica presente en todo momento, energía que es captada por las antenas del sistema y se manifiesta en ruido térmico presente a la entrada de los equipos. (Comparada con las demás fuentes, es de menor intensidad).

El ruido galáctico es debido a la energía procedente de las estrellas. Este ruido se tiende a ser de banda ancha, conteniendo componentes en una porción significativa del espectro. Otra fuente de ruido atmosférico son las tormentas eléctricas. Los rayos influyen mayormente en la región de HF (Altas frecuencias), por lo que puede recorrer grandes distancias.

La cantidad total de ruido adicional debido a estos tipos de fuentes se puede obtener con el uso de gráficos y/o tablas.

Matemáticamente esto puede expresarse como se describe a continuación:

$$N_{Tot} = KTBF.N_{Externo}$$

Ec.2.5.2

Dónde:

$N_{Tot}$  = Ruido total.

$N_{Externo}$  = Ruido externo debido a factores climáticos

Luego, despejando los parámetros conocidos, obtenemos que:

$$\frac{N_{Tot}}{KTR} = F.N_{Externo}$$

Ec.2.5.3

$$\frac{N_{Tot}}{KTR}dB = F_{dB} + 10\log(N_{Externo})$$

Ec.2.5.4

# Interferencia Cocanal – Múltiples Trayectorias:

Estas son dos interpretaciones del mismo problema, y se da cuando un sistema capta dos señales que se trasmiten a la misma frecuencia de portadora. La diferencia entre estas dos formas de interferencia se da si existe o no correlación con la señal transmitida. Es decir, si la señal interferente proviene de otra fuente, no presentará correlación, pero si la señal es la reflexión de la trasmitida, será una versión desplazada de la original, por lo que tendrá un determinado grado de correlación.

Los efectos que producen la interferencia cocanal y múltiple trayectoria, son distintos. Los múltiples caminos causan esencialmente una disminución de la señal producida por la diferencia de fase entre la señal directa y la reflejada. La interferencia cocanal produce perturbaciones aleatorias sobre la señal. Un ejemplo se da en las señales AM (Amplitud Modulada), cuando al receptor le llegan dos señales de frecuencia similar, pueden escucharse ambas al mismo tiempo. Pero generalmente si una es 6 dB mayor que la otra, no habría problemas.

# 2.6 RUIDO INTENCIONAL – CONTRAMEDIDAS ELECTRÓNICAS

Las contra medidas electrónicas son aquellos dispositivos que tienen como tarea engañar o burlar los sistemas de detección como el radar y sonar. Por lo tanto son fuentes de ruido de carácter intencional generado por el adversario, y poseen la dificultad de que por más que las señales interferentes sean trasmitidas por un aparato eléctrico, detrás de él se encuentra un conjunto de personas que aplican todos sus conocimientos para cumplir su objetivo.

Una de las fuentes intencionales más utilizadas y conocidas es el Jamming [3].

Mediante esta práctica su puede atacar al enemigo de dos maneras diferentes. Se puede negar el acceso a nuestra información, o se puede lograr que el adversario no pueda interpretar su información. Hay muchas maneras de hacerlo, como el camuflaje, el engaño, o la guerra. Esta última es la que ataca al adversario para negarle el transporte de información.

La técnica utilizada por el Jammer puede variar según la banda de frecuencias que se pretende afectar, el tiempo en que el jamming interfiere, o la información que pretende dañar [3]. Se explican algunas de estas técnicas a continuación.

# Jamming de banda ancha:

Consiste en introducir ruido en todo el rango de frecuencias en que esté operando el sistema. Es aplicable a cualquier tipo de señal.

# Jamming de banda angosta:

En este caso se trasmite energía a una determinada frecuencia para introducir ruido solo en un canal específico. La eficiencia de este método dependerá del nivel de conocimiento que se tenga de la señal a interferir.

# Jamming por tonos:

Se envía uno o varios tonos dentro del ancho de banda de la señal que se trasmita. Su eficiencia depende de cómo se introduzca el tono, lo que implica un gran estudio de la señal a interferir. Por ejemplo, si se trasmite un tono que se posicione sobre la frecuencia del uno, la fase del tono trasmitido debe coincidir con el de la señal, de lo contrario no producirá grandes efectos. Es decir, se logra interferir cuando se posiciona el tono en una frecuencia que represente un símbolo, y a su vez, respete su fase.

# Jamming por pulsos:

Señal interferente de banda ancha pero se trasmite solo en determinado instantes de tiempo. La eficiencia presenta características similares al Jamming de banda ancha. Permite ahorro de energía.

# Jamming por barrido:

Una vez introducido el ruido en una porción del espectro se sigue con un barrido en frecuencia sobre rango en que trabaje el sistema. Se utiliza en sistemas con FHSS (Espectro ensanchado por salto de frecuencia) para localizar la nueva frecuencia luego del salto. La velocidad del barrido debe ser lo suficientemente alta como para detectar el salto, pero no demasiado como para interferir una pequeña parte de la señal.

# 2.7 RUIDOS PROPIOS DEL RECEPTOR

El ruido es el factor principal que limita la sensibilidad del receptor, y es por ello que se hace un estudio detallado para describirlo cuantitativamente.

Por más que se considere un medio exento de todo tipo de ruido, y un trasmisor ideal que tampoco genere ruido internamente, va a existir en él una fuente generadora de ruido térmico debido al propio movimiento de los electrones.

Para receptores del tipo superheterodino, el ancho de banda del radar es prácticamente el ancho de banda de la frecuencia intermedia [2].

$$B_n = \frac{\int_{-\infty}^{\infty} |H(f)|^2 df}{|H(f_0)|^2}$$

Ec.2.7.1

Este ancho de banda no es el que comúnmente figura en la hoja de datos (a 3 dB de máxima potencia). H(f) es la respuesta en frecuencia de la etapa FI (filtro), y H(fo) es el valor máximo de la respuesta en frecuencia que generalmente es a la mitad de la banda. Cuando el valor normalizado de H(f) es igual a 1, Bn es llamado ancho de banda del ruido y es el ancho de banda de un filtro rectangular equivalente cuya potencia de ruido a la salida es igual a la del filtro con respuesta H(f).

El ancho de banda a 3 dB es muy usado y fácil de medir, pero el ancho de banda de ruido implica un conocimiento total de la respuesta H(f). Sin embargo, generalmente la respuesta en frecuencia de la mayoría de los filtros es tal que el ancho de banda a 3 dB y el ancho de banda de ruido no difieren apreciablemente. En la práctica se ve que la potencia de ruido medida difiere al valor del ruido térmico. Esto indica que existen otras fuentes de ruido y hay que tenerlas en cuenta.

El ruido total presente a la salida de un receptor puede ser considerado como la potencia de ruido térmico generada por un receptor ideal multiplicada por la figura de ruido del mismo.

$$F_n = \frac{N_0}{K.T_0.B_n.G_a}$$

Ec.2.7.2

$N_0$  es el ruido medido (en la parte lineal) a la salida del receptor, To es la temperatura estándar (290ºk),  $G_a$  es la ganancia (señal de salida( $S_0$ )/señal de entrada( $S_1$ )),  $B_n$  es el ancho de banda de la FI.

Si K.T<sub>0</sub>.B<sub>n</sub> es el ruido a la entrada, la ecuación 2.7.2 se escribe como,

$$F_n = \frac{S_i / N_i}{S_0 / N_0}$$

Ec.2.7.3

La figura de ruido se interpreta como una medida de la degradación de la relación señal a ruido cuando la señal pasa por el receptor.

Reordenando e igualando la ecuación 2.7.3 con la ecuación 2.7.2 se obtiene:

$$S_i = \frac{KT_0.B_n.F_n.S_0}{N_0}$$

Ec.2.7.4

$$S_{i-\min} = K.T_0.B_n.F_n.\left(\frac{S_0}{N_0}\right)_{\min}$$

Ec.2.7.5

La menor señal de entrada se corresponde con la mínima relación señal a ruido a la salida de la etapa FI del receptor.

Esta ecuación se utiliza en la ecuación del radar (Ecuación 2.4.7) para obtener el rango máximo del radar.

# **2.8** PROBABILIDAD DE DETECCION, PROBABILIDAD DE FALSA ALARMA Y RELACIÓN SEÑAL A RUIDO

En esta sección se detalla la teoría estadística del ruido para obtener la relación señal a ruido presente a la salida de filtro (Amplificador de FI, Frecuencia Intermedia), necesario para el cálculo de la probabilidad de detección sin exceder una probabilidad de falsa alarma preestablecida [3].

El ruido entrante en el filtro es asumido del tipo Gaussiano (Distribución Normal), con una función de densidad de probabilidad p(v) dada por:

$$p(v) = \frac{1}{\sqrt{2.\pi \cdot \varphi_0}} \cdot \exp\left(\frac{-v^2}{2\varphi_0}\right)$$

Ec.2.8.1

Donde do es la varianza, y el valor medio de v se toma como cero.

Ahora si se considera que el ruido pasa por un filtro de banda estrecha (Comparado con la FI), la densidad de probabilidad de la envolvente del ruido a la salida es:

Ecuación de Rice:

$$p(v) = \frac{R}{\varphi_0} \cdot \exp\left(-\frac{R^2}{2\varphi_0}\right)$$

Ec.2.8.2

Donde R es la amplitud de la envolvente del ruido a la salida del filtro.

Esta última ecuación es una forma de la función de densidad de probabilidad de **Rayleigh.** Esta distribución modela el desvanecimiento rápido de la envolvente de la señal, y es aplicable en casos de múltiples trayectorias.

La probabilidad de que la envolvente de ruido se encuentre entre los valores v1 y v2 es,

$$P(v1 \triangleleft R \triangleleft v2) = \int_{v1}^{v2} \frac{R}{\varphi_0} \exp\left(-\frac{R^2}{2\varphi_0}\right) dR$$

Ec.2.8.3

La probabilidad de que la envolvente de ruido exceda un valor V<sub>T</sub> (valor umbral), es

$$P(v_T \triangleleft R) = \int_{v_T}^{\infty} \frac{R}{\varphi_0} \exp\left(-\frac{R^2}{2\varphi_0}\right) dR = \exp\left(-\frac{{V_T}^2}{2\varphi_0}\right) = P_{fa}$$

Ec.2.8.4

Cada vez que el voltaje de entrada supera  $V_T$  se considera que fue detectado el objetivo, sin embargo la ecuación 2.8.4 establece la probabilidad de que el ruido supere también  $V_T$ , en otras palabras, es la probabilidad de falsa alarma. Esta probabilidad puede considerarse como la relación de tiempo en que la envolvente del ruido se encuentra sobre  $V_T$  y por debajo de  $V_T$ .

$$P_{fa} = \frac{1}{BT_{fa}}$$

Ec.2.8.5

Reemplazando en ecuación 2.8.4 se obtiene que:

$$T_{fa} = \frac{1}{B} \cdot \exp\left(\frac{V_T^2}{2\varphi_0}\right)$$

Ec.2.8.6

Por ejemplo, considerar un filtro con ancho de banda en FI igual a 1 MHz y un tiempo medio de falsa alarma permitido de 15 min, la probabilidad de falsa alarma es de 1.11 e-9. Usando la ecuación 2.8.4, el valor del umbral necesario para cumplir con ese tiempo es 6.45 veces el valor eficaz (rms) del ruido.

La ecuación 2.8.6 muestra una relación exponencial entre el tiempo de falsa alarma y el valor umbral. Una consecuencia de esto es que, suponiendo que la transmisión sea interrumpida y asumiendo que el tiempo medio de falsa alarma se mantiene igual, la probabilidad de falsa alarma incrementa considerablemente. Sin embargo no tiene mucha implicancia en la tensión umbral debido a esa relación entre ellas. Hasta ahora se ha supuesto que a la entrada del filtro sólo hay ruido. Considerar ahora una señal sinusoidal de frecuencia igual a la mitad de la banda de FI, sometida a este mismo ruido. A la salida del detector de envolvente se obtendrá una función de densidad de probabilidad dada por:

$$p_s(R) = \frac{R}{\varphi_0} \exp\left(-\frac{R^2 + A^2}{2\varphi_0}\right) I_0\left(\frac{RA}{\varphi_0}\right)$$

Ec.2.8.7

Donde  $I_0$  es la **función de Bessel** de orden cero con argumento RA/ $\phi$ o.

La ecuación 2.8.7 es llamada función de densidad de probabilidad de Rice, que es una generalización de la distribución de Rayleigh.

La distribución de Rice es utilizada para el modelado del desvanecimiento rápido de la señal en casos que exista una componente fuerte de ella, es decir un haz directo.

Ahora la probabilidad de detección es la probabilidad de que la envolvente R exceda el valor umbral.

$$P_d = \int_{M}^{\infty} p_s(R) dR$$

Ec.2.8.8

$$P_{d} = \int_{VT}^{\infty} \frac{R}{\varphi_{0}} \exp\left(-\frac{R^{2} + A^{2}}{2\varphi_{0}}\right) I_{0}(\frac{RA}{\varphi_{0}}) . dR$$

Ec.2.8.9

Esta integral no puede ser valuada por métodos simples, sino que es necesario realizar expansión en series para aproximar su valor, siempre y cuando se cumple con RA/ $\phi$ o>>1, A>>|R-A|.

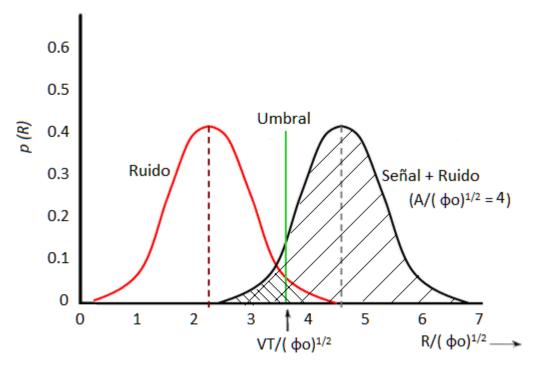

Otra solución es utilizar métodos gráficos como el que se muestra a continuación. La densidad de probabilidad de solo ruido (Ecuación 2.8.2) se muestra en la figura 2.8.1 junto con la de señal más ruido (Ecuación 2.8.9) con A/( $\phi$ o)<sup>1/2</sup>. Se establece un valor umbral VT/( $\phi$ o)<sup>1/2</sup> = 3,5.

Fig. 2.8.1 – Probabilidad de falsa alarma y probabilidad de detección.

El área sombreada a la derecha de VT/( $\phi$ o)<sup>1/2</sup> debajo de la curva señal más ruido representa la probabilidad de detección. El área doblemente sombreada debajo de la curva de solo ruido representa la probabilidad de falsa alarma. Como dijimos previamente, en el gráfico se ve que al aumentar el nivel umbral VT/( $\phi$ o)<sup>1/2</sup> la probabilidad de falsa alarma disminuye, pero también lo hace la probabilidad de detección.

La extensión en serie de la ecuación 2.8.2 se utiliza para graficar una familia de curvas que relacionan la probabilidad de detección con la amplitud de la señal. Aunque los diseñadores del receptor trabajan con niveles de tensión, a los ingenieros del sistema radar les son más útiles las relaciones de potencia. La extensión en serie puede ser convertida a potencia reemplazando relación señal a ruido (RMS) por lo siguiente:

$$\frac{A}{\sqrt{\varphi_0}} = \frac{Se\tilde{n}al}{Ruido_{rms}} = \frac{\sqrt{2}Se\tilde{n}al_{rms}}{Ruido_{rms}} = \left(2\frac{Se\tilde{n}al_{pot}}{Ruido_{pot}}\right)^{\frac{1}{2}} = \left(\frac{2N}{S}\right)^{\frac{1}{2}}$$

Ec.2.8.10

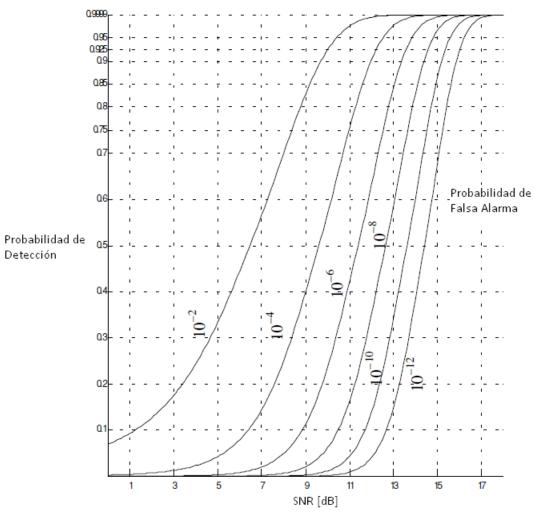

También se reemplazará VT/2  $\phi$ o por ln(1/ $P_{fa}$ ) [3]. Usando estas relaciones se grafica en la figura 2.8.2 la probabilidad de detección en función de la relación señal a ruido, y la probabilidad de falsa alarma como parámetro.

Fig.2.8.2 – Probabilidad de detección en función del SNR y la probabilidad de falsa alarma.

Tanto el tiempo de falsa alarma como la probabilidad de detección, especifican un determinado sistema.

Para utilizar el grafico primero se calcula la probabilidad de falsa alarma y luego con la ayuda del gráfico se obtiene la relación señal a ruido. Esta es la relación señal a ruido que se utiliza en la ecuación de la mínima señal detectable presentada anteriormente en la sección anterior.

Por ejemplo, si deseamos tener un tiempo de falsa alarma de 15 min y el ancho de banda de la FI es 1MHz, la probabilidad de falsa alarma es 1.1 e-9. Ingresando al gráfico se necesita una relación señal a ruido de 13,1 para una probabilidad de detección de 0,5. Una relación señal a ruido de 16,5 para una probabilidad de detección de 0,999.

Se puede concluir de la figura 2.8.2 que mientras más grande sea la señal comparada con el ruido, la detección es más probable que ocurra. Pero esto no puede decirse cuando se tiene en cuenta la probabilidad de falsa alarma. Del ejemplo desarrollado, se ve que un cambio en la relación señal a ruido de 3,4 dB, el sistema pasa de una probabilidad de detección de 0,5 a 0,999.

El cambio en el RCS es mucho más influyente en la relación señal a ruido que un cambio en la probabilidad de detección.

La relación señal a ruido requerida para la detección no es sensible al tiempo de falsa alarma.

# 2.9 TIPO DE SEÑALES DE RADAR.

El diseño de un trasmisor radar debe tener en cuenta una serie de puntos importantes a ser evaluados previo a la implementación del receptor.

El trasmisor debe proveer la suficiente energía como para que los ecos que lleguen al receptor permitan detectar el blanco. La forma en que ésta energía se trasmite depende del tipo de radar que se desea diseñar. Parámetros como potencia, frecuencia, ancho de banda, frecuencia de repetición de pulsos, ancho de pulsos, determinan el tipo de receptor que se deberá utilizar. Estos parámetros se deben fijar en función de la aplicación que se del sistema. En caso de una implementación real del sistema completo, se deben tener en cuenta aspectos como la dimensión de las antenas, peso de los mecanismos de funcionamiento y demás.

Existen dos grandes familias de radar que se distinguen por el tipo de señales que utilizan para su funcionamiento, el CW (Continuos Wave Radar – Radar de Onda Continua) y el PR (Pulse Radar – Radar Pulsado o de Pulsos). A partir de estas dos clases surgen distintos tipos de radares dependiendo, tal como se mencionó, de la aplicación que se le dé al mismo.

Claramente la principal diferencia entre las dos familias de radar es el modo de transmisión de la señal, uno lo hace de manera continua y el otro trasmite pulsos con determinada frecuencia de repetición. Dentro de los PR podemos encontrar radares de alta resolución, radares de seguimiento, radares de vigilancia, radares indicadores de objetivos en movimiento, radares doppler, radares de apertura sintética, entre otros. Todos ellos utilizan formas de onda pulsada a la cual se puede aplicarle algún tipo de codificación, modulación o compresión de pulsos según corresponda. Las técnicas de compresión de pulsos se describen en el capítulo 2.10.

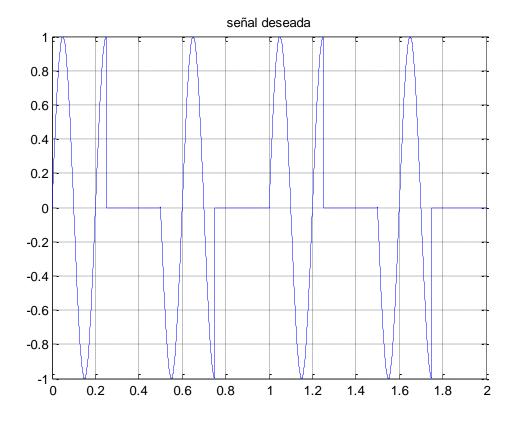

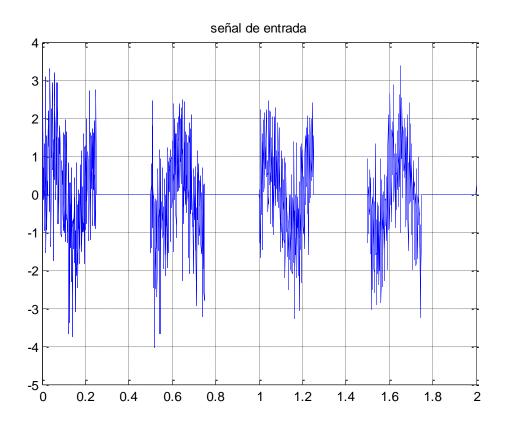

Para el cumplimiento de los objetivos en este trabajo, se utilizaron señales de pulsos compuestos por señales senoidales y modulación lineal de frecuencia. Esta forma de onda se denomina "Chirp".

Utilizar un chirp como señal transmitida implica realizar spread spectrum (Espectro expandido o ensanchado del espectro). El spread spectrum son técnicas que se utilizan en la transmisión de datos en radio frecuencias utilizando un espectro mayor que el que requiere el sistema para funcionar. El principal objetivo de estos métodos es coexistir de la mejor manera con la interferencia presente en el medio. También hace el sistema menos vulnerable respecto a usuarios no deseados.

Se utiliza un chirp con frecuencias comprendidas entre los 100 KHz y 9.375 MHz. No se realiza otro tipo de modulación ni se aplican métodos de codificación de la señal ya que no es aplicable a las pruebas determinantes del rendimiento realizadas en el modelo implementado.

## 2.10 COMPRESIÓN DE PULSOS.

Al comprimir el pulso que se va a trasmitir disminuye la potencia trasmitida lo que induce a una disminución de la relación señal ruido en el receptor. El rango de un radar se incrementa disminuyendo el ancho del pulso. Es decir, existe una relación de compromiso entre SNR y rango, ya que ambos parámetros varían según el ancho del pulso transmitido.

El objetivo de las técnicas de compresión de pulsos es lograr un ancho del pulso suficientemente grande para lograr una considerable potencia de trasmisión, pero no excederse para cumplir con requerimientos de rango.

# Producto tiempo - ancho de banda

En un sistema radar implementado con un filtro apareado, la potencia de ruido blanco dentro del ancho de banda del filtro viene dada por:

$$N_i = 2\frac{N_0}{2}.B = N_0.B$$

Ec.2.10.1

$N_0/2$  es la densidad espectral de potencia del ruido blanco. El factor 2 es para tener en cuenta las componentes + y – de frecuencia. La potencia media para un pulso de duración  $\tau$  es,

$$S_i = \frac{E}{\tau}$$

Ec.2.10.2

La relación señal ruido a la entrada del filtro apareado es,

$$(SNR)_i = \frac{S_i}{N_i} = \frac{E}{N_0.B.\tau}$$

Ec.2.10.3

La relación entre la SNR a la salida y la SNR presente a la entrada es,

$$\frac{(SNR)_{to}}{(SNR)_i} = 2B.\tau$$

Ec.2.10.4

Este resultado se refiere al producto tiempo ancho de banda para una determinada forma de onda, o su correspondiente Matched Filter.

El valor de  $B.\tau$  a partir del cual la SNR de la salida es mayor que la de la entrada, se denomina ganancia de compresión. Este producto puede incrementarse más allá de la unidad utilizando modulación en frecuencia.

Se presenta nuevamente la ecuación del radar, teniendo en cuenta el ruido blanco presente a su entrada.

$$\left(SNR\right)_{0} = \left(\frac{P_{t}.G^{2}_{tx}.\sigma.\lambda^{2}}{\left(4\pi\right)^{3}.L.k.T.B.R^{4}}\right)$$

Ec.2.10.5

Donde L son las pérdidas totales.

Las técnicas de compresión trasmiten pulsos relativamente anchos y procesa los ecos en pulsos angostos.

Se puede lograr que el pulso este constituido por muchos sub-pulsos cuyos anchos sean el deseado para la compresión.

Partiendo de la ecuación del radar,

$$(SNR)_{xc} = \frac{P_t \cdot \tau \cdot G^2_{tx.} \cdot \sigma \cdot \lambda^2}{(4\pi)^3 \cdot R^4 \cdot k \cdot T_e \cdot F \cdot L}$$

Ec.2.10.6

Donde

$$\tau = \frac{1}{B}$$

. Duración de

La ecuación para el pulso sin compresión puede escribirse como,

$$(SNR)_{x} = \frac{P_{t}.(\tau = n.\tau')G^{2}_{tx}.\sigma.\lambda^{2}}{(4\pi)^{3}.R^{4}.k.T_{s}.F.L}$$

Ec.2.10.7

Donde n indica el número de sub-pulsos de duración  $\tau'$  que componen el pulso trasmitido.

Para un conjunto de parámetros dados de Radar, la SNR permanece invariante siempre que no cambie el ancho del pulso, independientemente del ancho de banda.

El rango se mantiene invariante mientras que la resolución del rango mejora significativamente (  $\Delta R = \frac{c}{2B}$ ), manteniendo el ancho del pulso y aumentando el ancho de banda.

## 2.11 COMPRESION DE PULSO LFM.

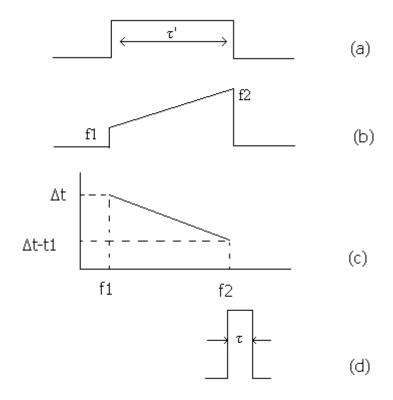

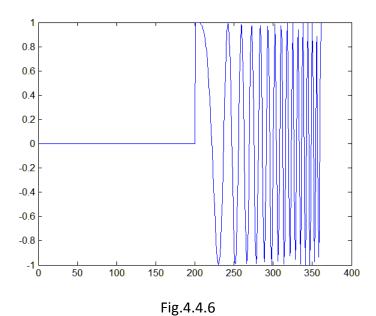

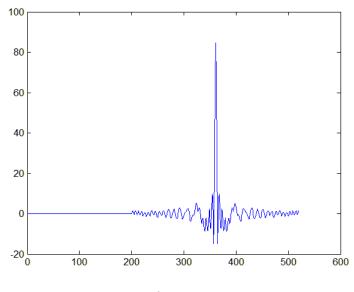

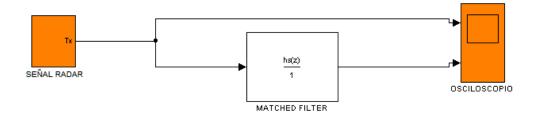

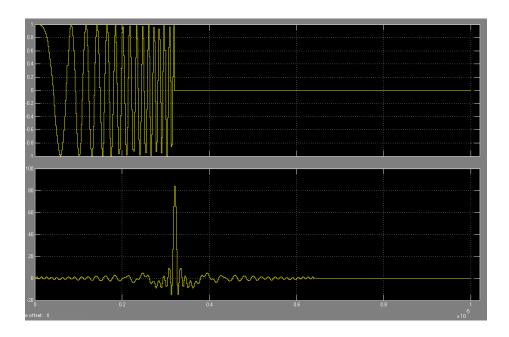

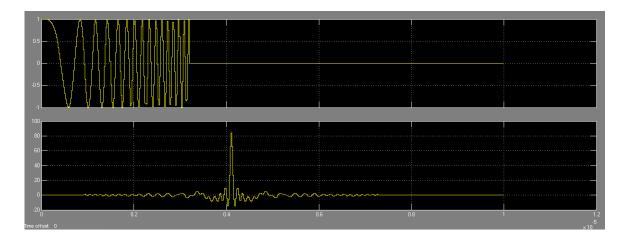

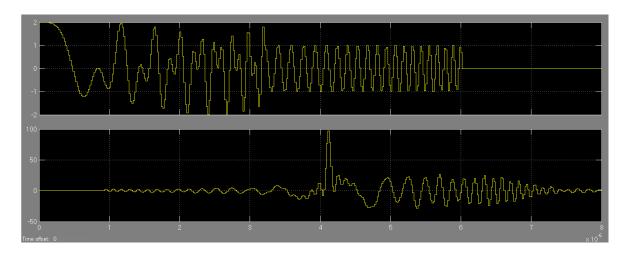

Esto se logra añadiendo modulación en frecuencia a un pulso largo que se trasmitirá, y usando un receptor con filtro apareado que permite la compresión del pulso. Como resultado, la salida del filtro se ve comprimida un factor  $\xi=B.\tau$ '. Entonces, utilizando pulsos largos y modulación LFM de banda ancha, grandes relaciones de compresión pueden ser logradas. En la figura 2.11.1 se muestra el proceso ideal de compresión.

Fig.2.11.1 – Proceso de compresión de pulso

La parte (a) muestra el pulso trasmitido, en (b) se ve la modulación en frecuencia, (c) muestra la característica que presenta el filtro respecto al retardo en el tiempo, y (d) es el pulso comprimido.

Para generar un pulso "chirp" con compresión lineal, la frecuencia justamente presenta relación lineal con el tiempo. La fase es función cuadrática.

La ecuación general que representa una con LFM es,

$$LFM = k.\cos\left(\pi \cdot \frac{B}{T}t^2 + \varphi\right)$$

Ec.2.11.1

Un sistema diseñado con filtro apareado y que utilice señales chirp reconocerá los elementos transmitidos, retrasará los resultados y mostrará un pulso comprimido con amplitud proporcional al eco recibido.

Para cumplir con objetivos de resolución es necesario aplicar métodos de ventaneo para reducir la influencia de lóbulos laterales.

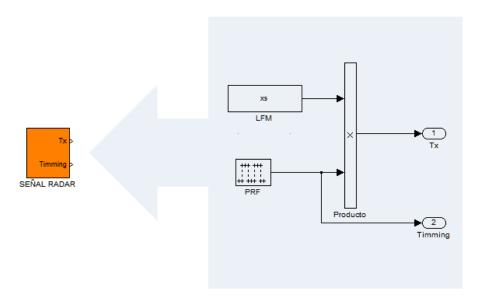

# 2.12 MODELO DE TRANSMISOR

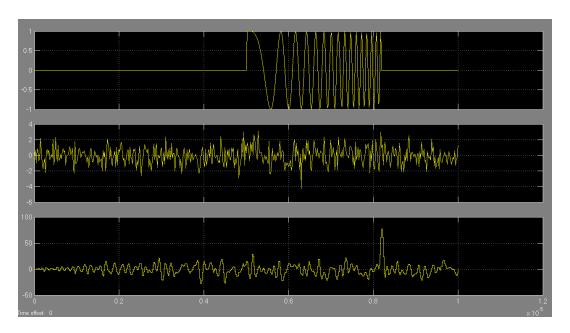

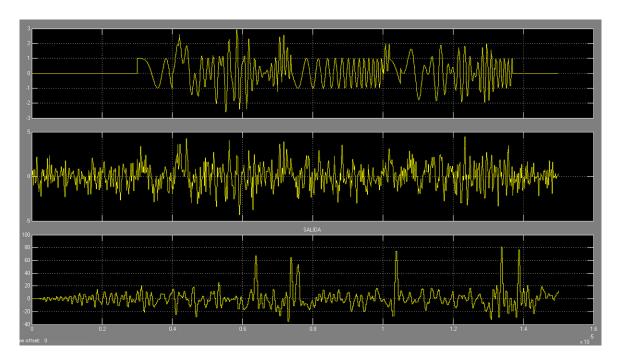

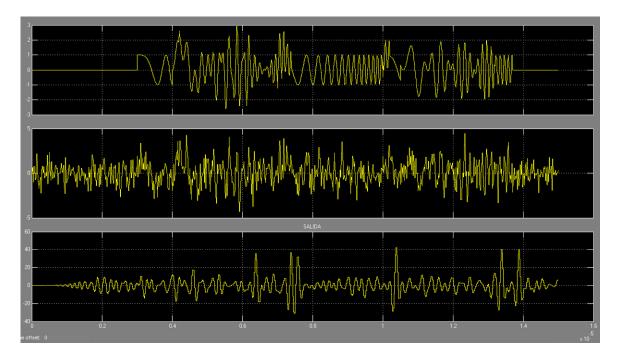

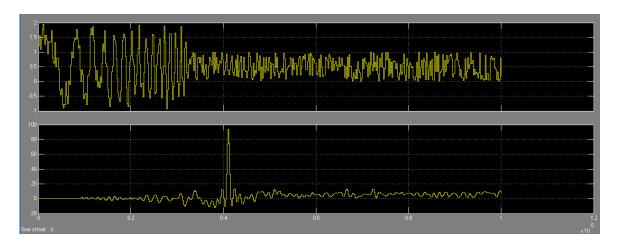

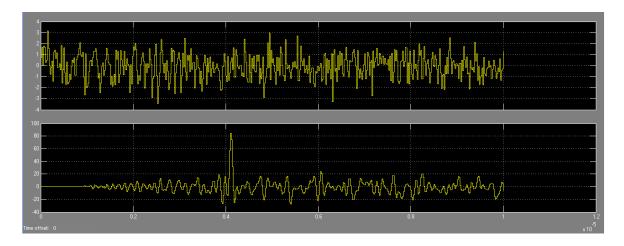

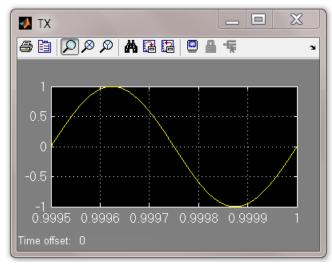

Según se describió en capítulos anteriores, sobre compresión de pulsos y LFM, se diseñó un modelo de trasmisor de radar pulsado con señal chirp, de 3.2 µs de duración y 9.375 MHZ de ancho de banda, cuyo diagrama en bloques se muestra en la figura 2.12.1.

Fig.2.12.1 – Modelo de transmisor radar en Matlab/Simulink

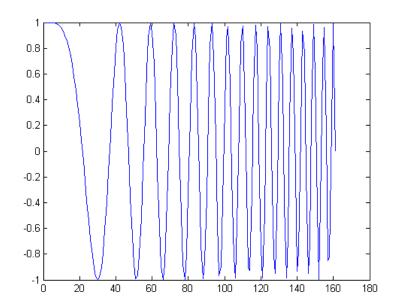

La siguiente figura ilustra la señal chirp generada por el transmisor de radar observado en la figura anterior.

Fig.2.12.2 – Pulso Chirp utilizado en el modelo de transmisor.

Considerando este modelo básico de trasmisor, fácilmente pueden lograrse las formas de onda necesarias para realizar pruebas determinantes del rendimiento del filtro.

Como se mencionó, no se agregan bloques de codificación o modulación extra.

## 2.13 TECNICAS DE VENTANEO.

Las técnicas de ventaneo o Windowing, limitan las señales a un número finito de muestras, lo que producen alteraciones en las componentes espectrales de las mismas. Una señal que muestra un impulso en el espectro, significa que es una señal continua en el tiempo y de única frecuencia. Al aplicarle algún tipo de ventana la amplitud del pulso disminuye considerablemente y surgen componentes espurias distribuidas en dicho espectro [4]. Esto produce dificultades para la detección de señales cuyas frecuencias sean próximas pero, en un principio, no es algo que influya significativamente en el tratamiento temporal de señales. La amplitud de un determinado eco depende de las características, dimensión y distancia respecto al receptor, del objetivo correspondiente. Por lo tanto pueden

darse casos en que el eco de un objetivo de gran porte o a menor distancia oculte el eco de otro objetivo.

Consideramos al ventaneo como una multiplicación,

$$x(n) = h(n).v(n)$$

Ec.2.13.1

Donde h(n) son los coeficientes del filtro, v(n) representa la ventana cuyas características dependen del tipo elegido, y x es la señal obtenida luego de aplicada la técnica de ventaneo.

Los tipos de ventanas clásicos utilizados para este fin son la de Hamming, Hanning, Triangular, Gaussiana, Kaiser, Bessel, Blackman, Harris, entre otras. Cada una de ellas con características aplicables a determinados sistemas [5].

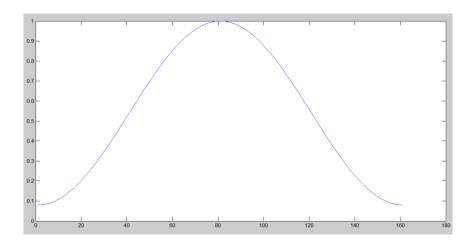

Se utilizó aquellas ventanas con las que se obtuvieron mejores resultados. Se presenta la ventana de Hamming en la siguiente ecuación:

$$v(n) = 0,53836 - 0,46164.\cos\left(\frac{2.\pi \cdot n}{N-1}\right)$$

Ec.2.13.2

Donde N es el tamaño de la ventana. La figura 2.13.1 ilustra la ventana de Hamming para un N = 161.

Fig.2.13.1 – Ventana de Hamming para N=161

En el capítulo 4 se describen las pruebas del filtro apareado aplicando las técnicas de ventaneo.

# 2.14 EL RECEPTOR RADAR

La función del receptor es detectar la señal deseada aun cuando ésta se encuentra interferida debido a diferentes fuentes de ruido, como lo son el jamming, ruidos ambientales o por clutter's. Es necesario separar la información útil, amplificarla hasta un determinado nivel necesario para ser procesada y por último ser entregada al usuario.

Un receptor no sólo se diseña teniendo en cuenta el tipo de señal que va a detectar, sino también la naturaleza del ruido, interferencia y los ecos de clutter con los que la señal deseada tendrá que competir.

El ruido puede penetrar al sistema a través de las antenas, o puede ser generado por el mismo receptor internamente. Generalmente utilizando microondas el ruido inevitable que entra por las antenas es menor que el del propio receptor, por lo que la sensibilidad de él se determina teniendo en cuenta esta última fuente de ruido.

Dependiendo del campo de aplicación del radar, se deberán realizar algunas propiedades y sacrificar otras capacidades para lograr el mejor funcionamiento posible para el que será diseñado. Los parámetros a tener en cuenta son ganancia, fase, estabilidad, rango dinámico, sintonización, confianza, estabilidad, entre otros. El receptor más utilizado es el superheterodino, debido a su buena sensibilidad, alta ganancia, selectividad y fiabilidad. Los factores determinantes de la sensibilidad del radar son la figura de ruido y la relación frente espalda (front-end en literaturas de habla inglesa).

Un buen diseño del receptor se debe centrar en maximizar la relación señal ruido a su salida y es aquí donde el algoritmo de Matched Filtering aplica sus capacidades para lograrlo. El filtro se incorpora en un módulo intermedio del receptor donde la señal ya pasó por un previo filtrado para acotar el ancho de banda de la señal de entrada, y en una instancia previa a la entrega de la información al usuario.

Para el desarrollo del modelo final del filtro aplicable al receptor radar se realizó una serie de estudios y pruebas previas los cuales sirvieron como experiencia necesaria para seleccionar el algoritmo y la estructura adecuada para el cumplimiento de los requerimientos de filtrado.

Se hace mención especial al algoritmo de filtrado adaptivo LMS [18][19], el cual se desarrolló en una primera instancia de aprendizaje durante este proyecto. La teoría de este filtro y las simulaciones realizadas se encuentran en el **Anexo A**, ya que no se consideró relevante incorporarlo en el cuerpo del informe, basados en los resultados y mediciones obtenidos.

Luego de esta etapa de aprendizaje y de numerosas pruebas, se desarrolló el filtro apareado descripto en los capítulos posteriores.

# **CAPÍTULO 3: PROCESAMIENTO DIGITAL**

# 3.1 INTRODUCCIÓN

El comienzo de la era de las comunicaciones surge con la invención del transistor. Dispositivo electrónico que dio lugar a los circuitos integradas de cada vez mayor escala de integración.

Como resultado de estos avances, los sistemas limitados en capacidad, rendimiento y eficiencia crecen a pasos agigantados, provocando una revolución en la forma de comunicación.

Cada vez se requieren mayores anchos de banda para traficar un gran volumen de información y todo esto en menores tiempos de procesamiento, implicando elevar las frecuencias de funcionamiento de los dispositivos y optimizar los recursos, provocando el calentamiento de los mismos hasta el límite de su destrucción.

La capacidad de representar un suceso de la naturaleza mediante una combinación de números binarios ofrece un gran poder de manipulación y transformación de estas señales y prácticamente realizar con ellas lo que se desee. Pero esta conversión analógica/digital tiene su precio, se incorporan errores de cuantificación y redondeo tanto al comienzo del procesamiento como al momento de entregar los datos al usuario para su evaluación, obteniendo como resultado una aproximación excelente (pero no exacta) a la realidad.

El procesamiento digital se utiliza en una gran cantidad de sistemas con propósitos y objetivos deferentes. Utilizando en cada caso plataformas y hardware acorde a la aplicación que se le dé.

En este capítulo se incorporan las estructuras existentes de filtro digital analizando ventajas y desventajas de cada uno de ellos. Seguido de las plataformas disponibles y la utilizada para este proyecto. Al final se dan a conocer las herramientas tratadas para realizar las simulaciones e implementación del modelo de filtro apareado.

# 3.2 FILTROS DIGITALES

En el ámbito del procesamiento analógico o digital de señales, el filtrado es una parte muy importante del sistema, ya sea para reducir el ancho de banda, eliminar componentes de frecuencia, restaurar o separar una señal.

El filtro analógico se caracteriza por tener un menor coste, mayor rapidez y un gran rango dinámico, pero el filtro digital ofrece otras ventajas, como por ejemplo sufren menor interferencia electromagnética, son estables frente a cambios de temperatura y al paso del tiempo, poseen alta precisión y por sobre todo son **programables**, lo que les da una gran versatilidad al momento de tratar con señales compuestas o variantes.

Un filtro digital manipula señales en tiempo discreto en base a una función de filtrado. Esta función es implementada mediante multiplicadores, sumadores y retardadores que combinan la señal de entrada con los coeficientes del filtro para

producir la señal de salida. La función de transferencia H(z) de un filtro digital es [14]:

$$H(z) = \frac{\sum_{k=0}^{M} b_k . z^{-k}}{\sum_{k=0}^{N} a_k . z^{-k}}$$

Ec.3.2.1

Los coeficientes  $a_k$  y  $b_k$  son los que determinan el tipo respuesta del filtro.

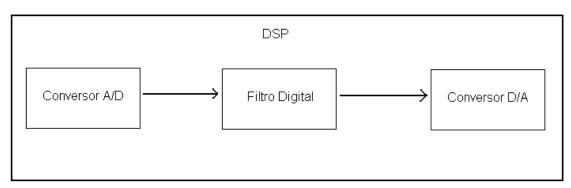

Como se mencionó, es un sistema en tiempo discreto, por lo que en caso de tener que filtrar una señal analógica, se debe proveer al sistema con conversores A/D y D/A, siempre respetando el teorema del muestreo (ver sección 3.7). En la figura 3.2.1 se muestra un esquema básico del filtrado digital. Al conjunto de sistemas utilizados para realizar el tratamiento de una señal digital se lo denomina generalmente DSP, acrónimo que significa Digital Signal Processing.

Fig.3.2.1 – Esquema básico de filtrado digital.

En el bloque "Filtro Digital" pueden incorporarse dos grandes familias de filtros, los FIR y los IIR.

Un filtro FIR (Respuesta Finita al Impulso) se caracteriza por tener respuesta finita al impulso, no tener retroalimentación y poseer todos los polos en el origen.

La primera propiedad significa que frente a una señal impulsiva de entrada el filtro responderá con una cantidad finita de términos no nulos. No posee retroalimentación ya que la salida solo se basa en el estado actual de las entradas del filtro. Y los polos en cero implican estabilidad.

A partir de la ecuación 3.2.1 y basados en sus características mencionadas, se llega a la función de transferencia del filtro FIR, dada por:

$$H(z) = \sum_{k=0}^{M} b_k . z^{-k}$$

Ec.3.2.2

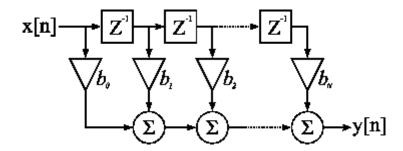

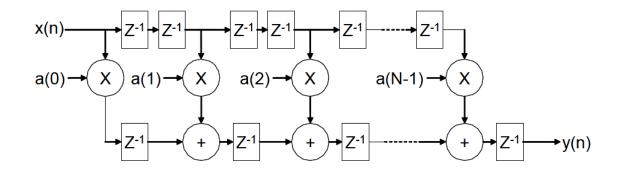

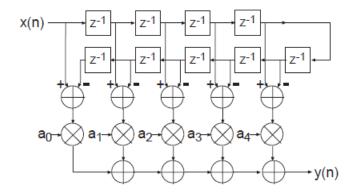

La estructura de implementación de este tipo de filtros se muestra en la figura 3.2.2 a continuación:

Fig.3.2.2 – Estructura de implementación de filtros FIR.

En la práctica, los filtros FIR se emplean en problemas de filtrado en los que se precisa una característica de fase lineal dentro de la banda de paso del filtro. A su vez, esta característica de fase lineal de los filtros FIR conlleva a un coste de mayor consumo de procesamiento, debido a la necesidad de mayor cantidad de coeficientes para lograr respuestas similares a un filtro IIR.

Los filtros IIR (Respuesta Infinita al Impulso) como su nombre lo indica poseen respuesta infinita frente a un impulso a la entrada, es decir, nunca vuelve al reposo. En este caso la salida del filtro depende tanto de las entradas presentes y pasadas como de las salidas en instantes anteriores. La función de transferencia H(z) de estos tipos de filtros es:

$$H(z) = \frac{\sum_{k=0}^{M} b_k . z^{-k}}{1 + \sum_{k=1}^{N} a_k . z^{-k}}$$

Ec.3.2.3

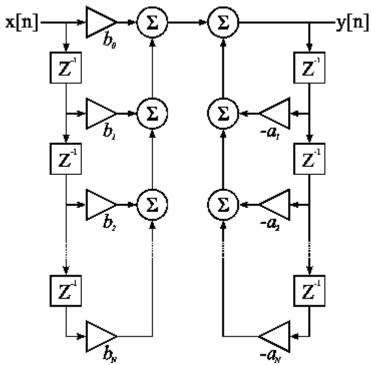

Y su estructura de implementación es la siguiente:

Fig.3.2.3 - Estructura de implementación de filtros IIR.

La ubicación de los polos y ceros determinarán la estabilidad y causalidad del sistema. Es normal pensar que este tipo de filtros requiera de un mayor espacio en memoria debido al mayor número de componentes para su realización, pero dado un determinado objetivo de filtrado, el filtro IIR posee un orden significativamente inferior comparado a un filtro FIR que cumpla con dichos objetivos.

Generalmente, los filtros IIR producen distorsiones en la señal procesada debido a sus características de fase no lineal en función de la frecuencia. Sin embargo, por regla general, un filtro IIR tiene lóbulos secundarios más pequeños en la banda de rechazo que un filtro FIR con el mismo número de coeficientes. Por esta razón, si es tolerable cierta distorsión, es preferible un filtro IIR, principalmente porque su implementación precisa muy pocos coeficientes, requiere menos memoria y presenta menos complejidad de cálculo.

El tipo de filtro que se emplee, ya sea FIR o IIR, depende de la naturaleza de las señales a tratar. En este proyecto en particular, se optó por la implementación de filtros FIR garantizando que todas las señales que se procesen sean tratadas por un filtro con características de fase lineal, evitando cualquier problema de distorsión que pueda ocurrir.

#### 3.3 FILTROS FIR

Como se mencionó anteriormente, los filtros FIR tienen repuesta finita al impulso, es decir que su salida frente a este estímulo es igual a un número finito de términos no nulos. La función de transferencia de estos filtros es la expresada en la ecuación 3.2.2 y debido a que sus polos están en el origen, estos filtros son siempre estables.

Si se considera al sistema causal, entonces la expresión siguiente caracteriza a un filtro FIR de coeficientes  $b_{\text{K}}$  en el dominio del tiempo:

$$h[n] = \sum_{k=0}^{M-1} b_k . \delta[n-k]$$

Ec.3.3.1

Donde  $\delta[n-k]$  representa el impulso unitario discreto y M es el número de coeficientes del filtro.

Alternativamente podemos expresar la salida y(n) como la suma de convolución de la respuesta impulsiva del sistema h(n) con la señal de entrada x(n).

$$y[n] = \sum_{k=0}^{M-1} h[k] x[n-k] = \sum_{k=0}^{M-1} b_k . x[n-k]$$

Ec.3.3.2

Las raíces de este último polinomio, como se puede observar, constituyen los ceros del filtro (donde la respuesta de esta función se hace cero).

Los filtros FIR son muy fáciles de realizar. La mayoría de los procesadores de señales digitales tienen unas arquitecturas internas que hacen factible su construcción.

#### ARQUITECTURA DE FILTROS FIR

Para su implementación en plataforma digital pueden utilizarse tres tipos de arquitecturas: algoritmo de Aritmética Distribuida y algoritmo de Multiplicadores Acumuladores en forma Directa y en forma Transpuesta [14].

El empleo de la aritmética distribuida (DA) para el procesado digital está justificado por su eficiencia de cálculo. La ventaja principal de la DA es su eficiencia de mecanización y la disminución de recursos internos que origina su utilización. Debido a que se trata de un proceso de naturaleza serie la desventaja que presenta es su relativa lentitud.

La aritmética distribuida (DA) es un método alternativo de realizar operaciones aritméticas que involucren la suma y el producto, en implementaciones software o hardware [7].

Dentro de las ventajas de la aritmética distribuida se encuentran su fácil y eficiente proceso de implementación, además de la reducción del número de compuertas usadas. La desventaja que se le puede adjudicar a la DA es su baja velocidad de respuesta, debido a su naturaleza serial; pero ésta se puede convertir en ventaja cuando se emplean diversas técnicas para mejorarla como: fraccionamiento de los datos de entrada y/o operación en forma totalmente paralela [7] [8].

La DA se ha usado principalmente en el procesamiento digital de señales cuando es requerida una suma de productos como la mostrada en la ecuación 3.3.3 Específicamente puede emplearse en el diseño e implementación de filtros digitales o en estructuras de diversas transformadas en el dominio de la frecuencia [7]. También es útil en sistemas de comunicaciones y en sistemas de control.

En la ecuación 3.3.3 se muestra una suma de productos, que define la respuesta de un sistema lineal e invariante en el tiempo. Donde y es la respuesta del sistema,  $X_K$  es la variable de entrada y  $A_K$  es un arreglo de coeficientes constantes.

$$y(n) = \sum_{k=1}^{k} A_k . x_k(n)$$

Ec.3.3.3

Si  $X_K$  es un número binario en complemento dos escalado, entonces  $X_K$  se puede expresar así:

$$x_k(n) = -b_{k0} + \sum_{n=1}^{N-1} b_{kn} \cdot 2^{-n}$$

Ec.3.3.4

Dónde  $b_{Kn}$  son bits (0 ó 1),  $b_{K0}$  es el bit de signo y  $b_{K\,N-1}$  es el bit menos significativo. Al reemplazar la ecuación 3.3.4 en la 3.3.3 y reordenando las sumatorias se llega a:

$$y(n) = \sum_{n=1}^{N-1} \left[ \sum_{k=1}^{k} A_k b_{kn} \right] 2^{-n} + \sum_{k=1}^{k} A_k - b_{k0}$$

Ec.3.3.5

Explícitamente, la ecuación 3.3.5 puede darse en términos de los todos los productos y sumas parciales de la siguiente forma:

$$\begin{split} y &= - \big[ x_{10}.A_1 + x_{20}.A_2 + \ldots + x_{k0}.A_k \, \big] + \big[ x_{11}.A_1 + x_{21}.A_2 + \ldots + x_{k1}.A_k \, \big] 2^{-1} \\ &+ \ldots \ldots + \big[ x_{1(B-2)}.A_1 + x_{2(B-2)}.A_2 + \ldots + x_{k(B-2)}.A_k \, \big] 2^{-(B-2)} \\ &+ \big[ x_{1(B-1)}.A_1 + x_{2(B-1)}.A_2 + \ldots + x_{k(B-1)}.A_k \, \big] 2^{-(B-1)} \end{split}$$

Ec.3.3.6

Si es observado el término en los corchetes de la ecuación 3.3.5, esta expresión posee 2<sup>K</sup> posibles valores como lo demuestran los términos en los corchetes de la ecuación 3.3.6. Luego se pueden calcular estos valores y almacenarlos en una memoria o DALUT (Distributed Arithmetic Look Up Table por sus siglas en inglés); con lo cual se evita el cálculo de los productos parciales en tiempo real. Los datos de entrada son usados para direccionar la DALUT, y la salida es guardada en uno o varios registros para ser sumados usando desplazamientos denotados por los factores exponenciales en la ecuación 3.3.6 y obtener de esta manera el resultado final. Como ejemplo del contenido de una DALUT es mostrada la Figura 3.3.1.

| 0            |

|--------------|

| A1           |

| A2           |

| A1 + A2      |

| A3           |

| A1 + A3      |

| A2 + A3      |

| A1 + A2 + A3 |

Fig 3.3.1 - Contenido de una DALUT con K=3.

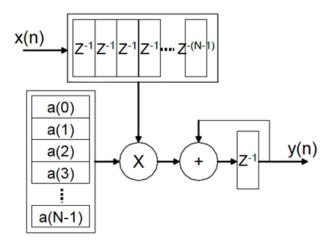

Otro algoritmo de implementación del filtro FIR, se denomina MAC (Multiply Accumulate). Éste implica que se realiza el computo de cada producto entre los  $b_K$  y la señal x(n) con su correspondiente retraso, donde cada uno de esos resultados parciales se va acumulando hasta realizarse los M productos necesarios para obtener una muestra de señal de salida y(n). Para la obtención de cada muestra y(n), se necesitan M multiplicaciones y M - 1 sumas de forma recursiva.

Una visión simplificada de un FIR MAC basada en la utilización de un solo motor MAC se muestra en la figura 3.3.2.

Fig.3.3.2 – Diagrama en bloques de un FIR con MAC simple.

La puesta en práctica de extensiones Multi-MAC sólo es requerida para implementaciones de filtros de altos requerimientos (un mayor número de coeficientes, tasas más altas de muestreo, más canales, etc.)

El número de multiplicadores necesarios para aplicar un filtro se determina calculando el número de multiplicaciones necesarias para realizar el cálculo (teniendo en cuenta la simetría de la estructura de coeficiente y los cambios de frecuencia de muestreo) y dividiendo por el número de clock´s disponibles para procesar cada entrada de una muestra.

El número de clock's necesarios siempre se redondea hacia abajo y el número de multiplicadores se redondea al entero más cercano. Si al realizar el cálculo  $F_{CLK}/F_s*N$ úmero de Canales hay un resto distinto de cero, algunos de los motores MAC hará el cálculo con menos coeficientes que los otros, y los coeficientes de éste se rellenan con ceros para evitar respuestas erróneas del filtros.

En la implementación del filtro se genera automáticamente una aplicación que cumple con los requisitos de desempeño definidos por el usuario basado en la velocidad del clock del sistema, la frecuencia de muestreo, el número de canales, y la tasa de cambio.

En la figura 3.3.3 se muestra una estructura MAC de forma Directa.

Fig.3.3.3 - Estructura Directa de un Filtro FIR.

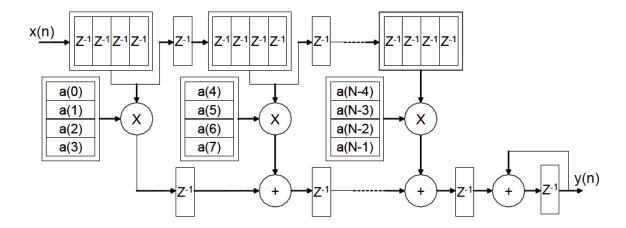

La Figura 3.3.4 muestra una implementación Multi-MAC para esta arquitectura.

Fig.3.3.4 - Estructura Directa de un filtro FIR Multi-MAC.

La arquitectura directa permite implementaciones con uso eficiente de área (Consumo de recursos) y alto desempeño del filtro. Esta estructura se aplica también para explotar la simetría de los coeficientes ofreciendo ahorro de recursos.

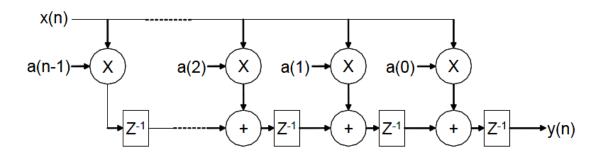

Otro tipo de arquitectura común en filtros FIR es la llamada estructura Transpuesta, la cual puede derivarse de la estructura Directa sin más que modificar la posición de los elementos de retardo tal como se ilustra en la figura 3.3.5. La ventaja de cambiar el orden de dichos elementos permite aprovechar la técnica de pipelining. El pipelining es una técnica en diseño computacional y electrónico, que permite descomponer un proceso en múltiples pasos intermedios, siendo la salida de uno la entrada del próximo paso, interponiendo registros en las entradas y salidas de dichos pasos intermedios. Esto permite trabajar a velocidades de clock mayores, lo que da como resultado una velocidad mayor de procesamiento final en el proceso completo.

Fig. 3.3.5 - Estructura Transpuesta de un filtro FIR.

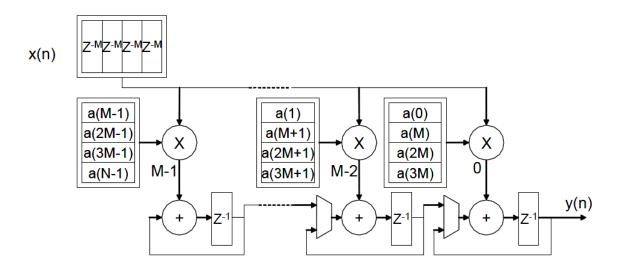

La figura 3.3.6 muestra una implementación Multi-MAC para esta arquitectura.

Fig. 3.3.5 - Estructura Transpuesta de un filtro FIR Multi-MAC.

Esta estructura ofrece una aplicación de baja latencia, y para algunas configuraciones también puede ofrecer un ahorro de recursos adicionales sobre la estructura Directa. No requiere de un acumulador y se puede utilizar menos recursos de memoria de datos, a pesar de que no se aprovecha la simetría de los coeficientes, lo cual se describe a continuación.

#### **COEFICIENTES**

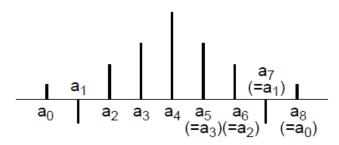

La respuesta al impulso de los filtros FIR posee simetría significativa. Esta simetría en general, puede ser explotada para minimizar los requisitos de implementación, optimizando la cantidad de recursos utilizados del hardware. La figura siguiente muestra la respuesta al impulso para un filtro FIR de coeficientes simétricos de 9 etapas.

Fig.3.3.6 – Respuesta simétrica al impulso.

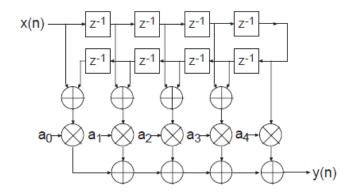

En lugar de aplicar este filtro, utilizando la arquitectura mostrada en la figura 3.3.3, se puede utilizar una estructura más eficiente, tal como se muestra en la figura 3.3.7. En general, el enfoque anterior requiere M multiplicaciones y (M-1) sumas. En contraste, la arquitectura en la Figura 3.3.7 sólo requiere [M/2] multiplicaciones y M sumas. Esta reducción significativa en la carga de trabajo computacional puede ser explotada para generar implementaciones más eficientes en el hardware.

Fig.3.3.7 - Arquitectura para un número par de coeficientes.

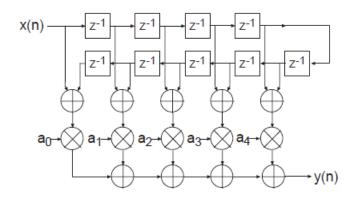

Fig. 3.3.8 - Arquitectura para un número impar de coeficientes.

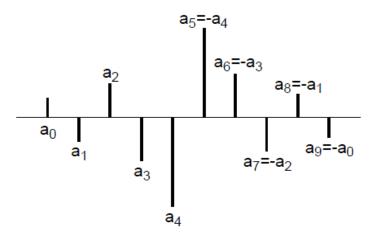

La figura 3.3.9 muestra la respuesta al impulso de un FIR con simetría negativa, o impar.

Fig.3.3.9 - Respuesta al impulso con simétrica negativa.

Esta simetría es fácil de explotar de una manera similar a la mostrada en la figura 3.3.7 y en la figura 3.3.8. En este caso, los sumadores son sustituidos por una combinación de sumadores y restadores, como se ilustra en la figura 3.3.10.

Fig.3.3.10 – Arquitectura de un FIR con simétrica negativa

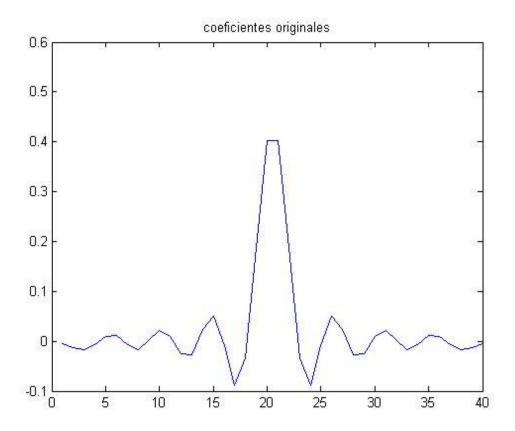

En el desarrollo de este TFG se utilizó un filtro FIR con coeficientes no simétricos, implementado con multiplicadores y acumuladores en forma transpuesta debido a que permite incrementar la performance del filtro a frecuencias elevadas.

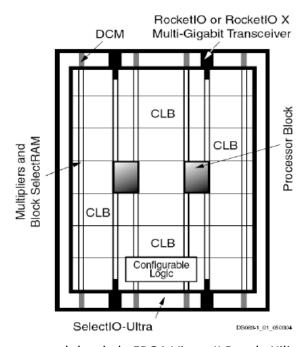

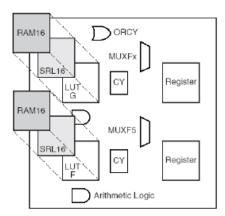

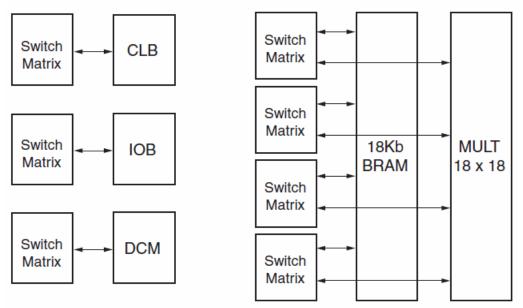

#### **3.4** PLATAFORMAS DIGITALES

Los filtros digitales tienen la gran ventaja de poder ser diseñados, simulados e implementados desde un computador para finalmente ser implementados en una plataforma digital.

Existen tres categorías fundamentales de dispositivos de hardware que permiten implementar algoritmos de procesamiento digital de señales: DSPs, FPGAs y ASICs. Estos dispositivos constituyen componentes de hardware, siendo su elección un compromiso entre flexibilidad, capacidades de procesamiento y consumo de potencia.