# Implementación de un Modulador QPSK de Cuatro Salidas para la Conformación de Haz de Radiación Variable en Tiempo Real

Javier F. Fernández, Gabriel Caballero, Pablo Sonna, Marcela Busnardo

Departamento Electrónica y Telecomunicaciones, Especialidad en Sistemas Embebidos.

Facultad de Ingeniería

Instituto Universitario Aeronáutico

Córdoba, Argentina

Emails: jffernandez, gcaballero, psonna, mbusnardo@iua.edu.ar

Resumen— La conformación de un haz de radiación en el campo de antenas inteligentes se lleva a cabo alimentando cada una de las antenas de un arreglo con una fase específica, es decir una variación temporal de la señal. El objetivo de este trabajo es el de implementar sobre una arquitectura FPGA cuatro moduladores QPSK de fase variable entre 0 y  $2\pi$ , en tiempo real, con frecuencia de portadora en 500KHz, que modulen la misma fuente de información obteniendo cuatro señales moduladas con una portadora de una fase específica para la implementación de un sistema de antenas de dimensión 2x2.

Antenas, arreglos, radiación, FPGA, implementación, modulador, PSK.

## I. INTRODUCCIÓN

El uso de arreglos de antenas para la conformación de un haz de radiación en una dirección deseada, está siendo utilizado en diversos campos de aplicación debido a la versatibilidad que proporciona el avance de la tecnología. En un arreglo de múltiples antenas, la conformación de un haz de radiación en una dirección especifica, se logra variando la fase de la señal que alimenta a cada antena de forma individual. El campo radiado de un arreglo de antenas de dimensión 2x2 se da por la siguiente función, extraída de [1]:

$$\begin{split} E_{22} &= \left(\frac{1}{4}\right) \left[ a_{11} e^{+j\beta (d_x \psi_x + d_y \psi_y)} + a_{1-1} e^{+j\beta (d_x \psi_x - d_y \psi_y)} + a_{-11} e^{+j\beta (-d_x \psi_x + d_y \psi_y)} + a_{-1-1} e^{+j\beta (-d_x \psi_x - d_y \psi_y)} \right] \ (1) \end{split}$$

Donde E es el campo electromagnético resultante, los coeficientes a, refieren a la ubicación de cada antena dentro del arreglo y donde  $\psi_x$  y  $\psi_y$  son los angulos de direccion del haz de radiación que se desea obtener.

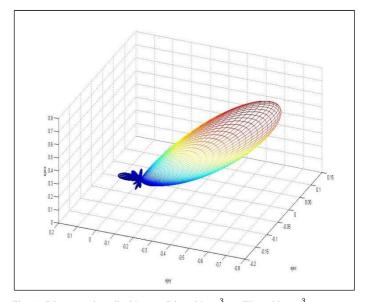

En la figura 1 se presenta un diagrama de radiación desarrollado con (1) para una dirección específica.

Fig. 1. Diagrama de radiación para Dirección =  $\frac{3}{4}\pi$  y Elevación =  $\frac{3}{4}\pi$

Generalmente la forma de lograr estos desfasajes individuales es utilizando algún elemento capaz de variar la amplitud y la fase de la señal modulada proveniente del modulador. El procesamiento de la señal en dicha etapa de modulación, requiere de equipos de elevado costo y complejidad [2],[3]. Una alternativa para evitar el uso de estos equipos es generar los desfasajes en una frecuencia intermedia dentro de la cadena del transmisor. Si además se agrega que la generación de la portadora se realiza de forma digital utilizando técnicas de síntesis de señales, se pueden generar desfasajes de forma digital.

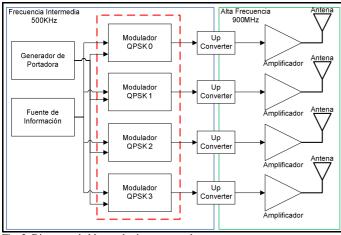

En la figura 2 se muestra un diagrama de bloques del sistema de antenas inteligentes para un arreglo de dimensión 2x2. Como se puede ver, la generación de portadora y la modulación con portadoras desfasadas se realiza en frecuencia intermedia, luego se lleva a alta frecuencia para amplificar antes de la salida a antenas. Este trabajo está ubicado en el ámbito de los moduladores QPSK resaltados con línea de puntos.

Fig. 2. Diagrama de bloque de sistema completo

#### II. DESARROLLO

En este trabajo se utiliza los conocimientos adquiridos en la presentación de un modulador QPSK introducido en [4] con el objetivo de implementar de una modificación del mismo que permite la integración de cuatro y posteriormente N moduladores de este tipo sobre una plataforma FPGA.

La arquitectura a implementar consiste en la generación de cuatro portadoras con su correspondiente desfasaje, que luego serán utilizadas como señal modulante.

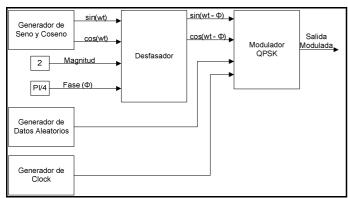

En la figura 3 se presenta el diagrama de bloques del modelo de modulador QPSK a implementar, el sistema final consta de 4 moduladores de este tipo en funcionamiento simultáneo, cada uno con su correspondiente desfasaje.

Fig. 3. Diagrama de bloques de esquema modulador QPSK

A continuación se pasa a detallar el funcionamiento de cada uno de los bloques del modulador, acompañado de las formas de onda obtenidas de la simulación de cada uno de ellos.

# a. Generador de Seno y Coseno

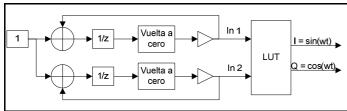

En la figura 4 se muestra el diagrama de bloques del generador de seno y coseno implementado en el modulo sin\_source en lenguaje Verilog.

Fig. 4. Diagrama de bloques del generador de seno y coseno

Este modulo está formado por una LUT (Look Up Table por sus siglas en inglés) que contiene los valores correspondientes a un cuarto de ciclo de la función coseno, esta LUT, está alimentada por un integrador que recorre los valores requeridos para formar un ciclo completo de la función coseno. La LUT contiene lógica agregada para devolver por la salida seno y coseno los valores correspondientes para formar el ciclo completo de coseno o seno a partir de un cuarto de ciclo de coseno. Variando el incremento del integrador, se puede variar la frecuencia de la señal de seno y coseno de la salida de la LUT. Además la variación del valor inicial del integrador sirve para ajustar la fase de las señales obtenidas de la LUT. En este punto la variación del incremento de integrador y del valor inicial se utilizan para el primer ajuste de frecuencia y fase de la señal portadora.

#### Generador de datos aleatorios

El Generador de datos aleatorios es un BBG (Bernoulli Binary Generator por sus siglas en inglés) que genera una secuencia de bits pseudo aleatorio. Este generador consiste en un shift register realimentado de 7 bits y es usado como la fuente de información, es decir los datos a modular.

#### c. Desfasador

La función de este modulo es la de escalar y desfasar las portadoras I y Q obtenidas del generador de portadoras. Expresando las portadoras I y Q como una señal compleja del tipo  $e^{j\omega t}$ , entonces para lograr el desfasaje, se debe multiplicar esta función por  $Ae^{-j\phi}$ , siendo  $\phi$  el ángulo por el que se quiere desfasar la portadora y A la amplitud. Al descomponer esta funcion en parte real e imaginaria, la parte real I queda:

$$A\cos\omega_c t\cos\phi + A\sin\omega_c t\sin\phi = A\cos\omega_c t - \phi$$

(2)

Y la parte imaginaria Q resulta:

$$A \sin \omega_c t \cos \phi - A \cos \omega_c t \sin \phi = A \sin \omega_c t - \phi (3)$$

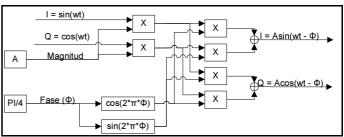

Estas últimas dos funciones son las implementadas en el desfasador cuyo diagrama de bloques se muestra a continuación en la figura 5.

Fig. 5. Diagrama de bloques de desfasador de señales I y Q

# d. Modulador OPSK

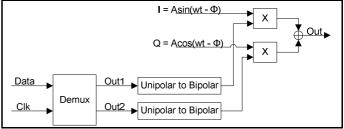

En la figura  $N^{\circ}6$  se presenta el diagrama de bloques del modulador QPSK

Fig. 6. Diagrama de bloques del modulador QPSK

El modulo demultiplexor (Demux) o conversor serie/paralelo, recibe datos en forma serial y los agrupa en palabras de dos bits. Los datos que salen del Demux se convierten de unipolar a bipolar, el cual devuelve un -1 para el valor de entrada 0 y un 1 para el valor de entrada 1. Uno de los datos ingresados se multiplica por la componente  $I = A\sin(\omega_c t - \phi)$  de señal y el otro dato por la componente  $Q = A\cos(\omega_c t - \phi)$ .

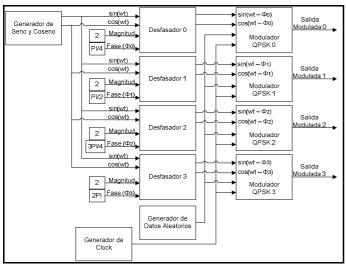

### e. Circuito Final

En la figura 7 se presenta el diagrama de bloques del circuito final que incluye los cuatro moduladores, como se puede observar en la figura, solo es necesario un generador de seno y coseno, pero es necesario cuatro desfasadores y cuatro moduladores para obtener las cuatro señales moduladas desfasadas.

Fig. 7. Diagrama de bloque del sistema implementado

## III. SIMULACIÓN

En esta sección, se presentan las señales adquiridas de la etapa de simulación mediante testbench de la implementación en Verilog y se comparan con las señales adquiridas en simulación con la herramienta de MATLAB, Simulink. Esta simulación se realiza sobre el código Verilog implementado, por esto su importancia.

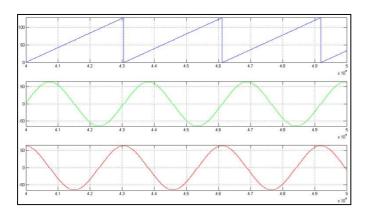

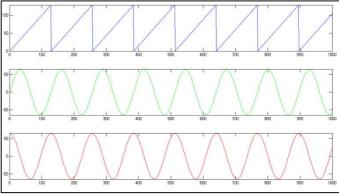

En la figura 8 se presentan las señales provenientes del generador de seno y coseno. La primer señal es la salida del integrador, en la figura se puede observar una señal del tipo diente de sierra que varía entre los valores 0 y 128 para recorrer la LUT del generador. En la segunda y tercer señales de la figura se pueden observar las salidas de la LUT, en la segunda señal, la salida seno y en la tercer señal la salida coseno, ambas señales representadas con 7bits

Fig. 8. Salida del integrador, señal seno y señal coseno implementado

En la figura 9 se presenta su comparación adquirida con Simulink.

Fig. 9. Salida del integrador, señal seno y señal coseno simulado

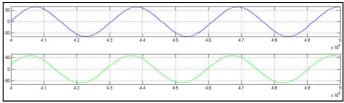

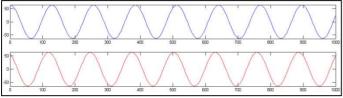

En la figura 10 se muestra la señal de entrada al desfasador y la señal de salida con un desfasaje  $\phi$  aplicado de  $\frac{1}{9}\pi$ . La primera señal de la figura 10 corresponde a la segunda señal de la figura 8

Fig. 10. Entrada y salida de la señal seno al desfasador implementado

En la figura 11 se presenta su comparación adquirida con Simulink.

Fig. 11. Entrada y salida de la señal seno al desfasador simulado

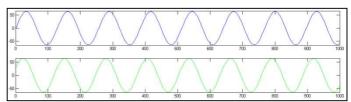

Así mismo, en la figura 12 se muestra la señal de entrada al desfasador y la señal de salida con un desfasaje  $\phi$  aplicado de  $\frac{1}{9}\pi$ . La primera señal de la figura 12 corresponde a la tercera señal de la figura 8

Fig. 12. Entrada y salida de la señal coseno al desfasador implementado

En la figura 13 se presenta su comparación adquirida con Simulink.

Fig. 13. Entrada y salida de la señal coseno al desfasador simulado

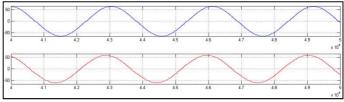

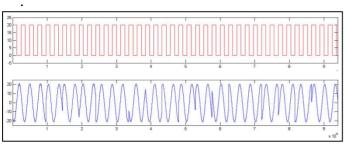

En la figura 14 se presentan las señales obtenidas a del modulador QPSK, la primer grafica se puede observar la señal de clock del sistema, y en la segunda la señal modulada. Para comprender mejor esta última, cabe recordar que cada símbolo está formado por dos bits, por lo que cada símbolo tiene por duración dos ciclos de clock

Fig. 14. Señal de clock y señal modulada QPSK implementada

En la figura 15 se presenta su comparación adquirida con Simulink.

Fig. 15. Señal de clock y señal modulada QPSK implementada

# IV. IMPLEMENTACIÓN

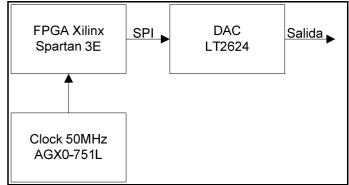

El sistema se implementa en una Spartan 3E Starter Kit Board que cuenta con una FPGA Xilinx XC3S500E de la familia Spartan 3E de 500K gates de capacidad, equipada con un oscilador de 50MHz a travez de un integrado AGX0-751L. La placa también está equipada con un conversor AD/DA de 12 bits de 2 Mega Samples por segundo de 4 canales con interface de comunicación SPI, implementada con un integrado LT2624 de Linear Tech. Estos son los tres aspectos técnicos más importantes a considerar para la implementación del sistema presentado. Estas características técnicas llevaron al desarrollo de un modulo para el tratamiento del clock para llevarlo a la frecuencia deseada y un modulo para el manejo de la interface SPI para el manejo del conversor DA. En la figura N° 16 se presenta un diagrama de bloques del hardware donde se implementa el sistema.

Fig. 16. Diagrama en bloques de Hardware de implementacion.

El clock de 50MHz es dividido por un factor de 10 para representar un periodo de la portadora de 500KHz con 10 muestras por periodo. Este hecho y las características técnicas del conversor DA, de poseer una interface de comunicación SPI, que requiere de 24 ciclos de clock para convertir una muestra, limita la cantidad de señales de 500KHz que se pueden generar en simultaneo en el conversor DA a una sola. Este problema limita la implementación final del sistema pero es suficiente para comprobar la correcta implementación del sistema.

En la figura 17 se presenta el escenario de prueba que está compuesto por la placa de desarrollo Spartan 3E Starter Kit conectado a un osciloscopio a la salida analógica del conversor DA. Para las distintas pruebas, se cambia la señal de entrada al conversor DA para poder ver señales en las distintas etapas del sistema.

Fig. 17 Escenario de prueba

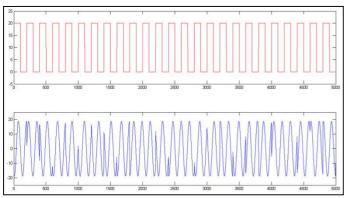

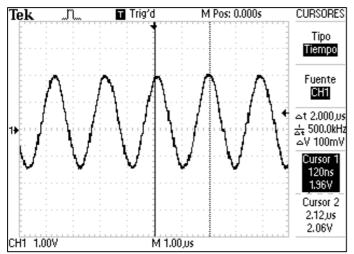

La primera prueba consiste en verificar que la frecuencia de la portadora generada, es específicamente de 500KHz, con esto se prueba que el factor de división del clock y el salto del contador que indica la posición de memoria de la LUT a leer, han sido correctamente calculados. Nuevamente, como las limitaciones técnicas del conversor DA, solo nos permite conformar una señal de 500KHZ, solo se mostrará la señal de portadora seno generada. Esto es suficiente para asegurar que la señal coseno generada es de la misma frecuencia. La figura 18 muestra la señal registrada de osciloscopio de la señal seno generada para usar de portadora del modulador.

Fig. 18. Señal seno salida de generador de seno y coseno registrada del osciloscopio

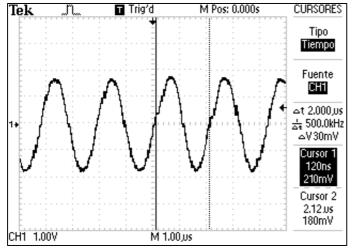

La segunda prueba consiste en verificar que el desplazamiento en fase aplicado en el modulo Phase Shifter no genera una variación en la frecuencia ni una deformación de la señal senoidal. La prueba fundamental en este punto seria poder comparar la señal antes y después del proceso de desfasaje para comprobar el correcto funcionamiento de dicho modulo, nuevamente, las limitaciones técnicas del conversor nos impiden realizar esta comparación, por lo que en este caso, el correcto funcionamiento del modulo queda verificado por la simulación presentada en la sección anterior. La figura 19 muestra la salida de la señal seno del desfasador de señal.

Fig. 19. Salida del desfasador de la señal seno registrada en osciloscopio.

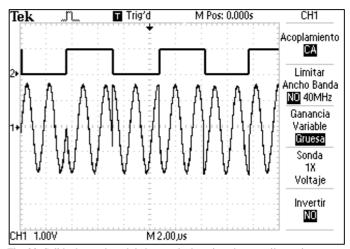

La tercera prueba consiste en la visualización en osciloscopio de la señal modulada junto con la señal de clock. En este caso, la señal modulada es la señal de salida del sistema a través del conversor DA. La señal de clock, es una señal digital, extraída mediante una pin de entrada salida de la placa de desarrollo. La figura 20 muestra la salida obtenida del osciloscopio para esta prueba.

Al igual que en la etapa de simulación, se puede observar las distintas fases para cada conjunto de datos, además, en esta figura, la frecuencia de clock del sistema así también como la frecuencia de la portadora en cualquiera de las fases moduladas es de 500KHz.

Fig. 20. Salida de señal modulada con clock registrada en osciloscopio

### **V. CONCLUSIONES**

De la implementación de este sistema y de las pruebas realizadas se puede concluir que se ha cumplido con los objetivos propuestos para el presente trabajo. Se ha logrado implementar un sistema de cuatro moduladores QPSK con una frecuencia de portadora de 500KHz de fase variable en tiempo real independiente para cada modulador.

Se ha comprobado el correcto funcionamiento de la implementación del sistema con simulación en etapa de síntesis, comparada con el modelo de simulación de Simulik y luego con la obtención de imágenes a través de osciloscopio, que comprueba el correcto funcionamiento en la etapa de implementación.

## VI. TRABAJO FUTURO

Con respecto a las limitaciones técnicas nombradas anteriormente del conversor DA, que solo posibilita la generación de una sola señal analógica de 500KHz simultanea, el principal aspecto a solucionar es el de desarrollar hardware que pueda ser conectado a las IO digitales de la placa para poder generar las cuatro señales moduladas simultaneas, por ejemplo un hardware que posea un conversor DA con las características técnicas necesarias para solucionar el problema o múltiples conversores DA como los usados que trabajen en paralelo, con cuatro interfaces SPI de comunicación.

El segundo aspecto técnico a solucionar es la determinación en tiempo real de las fases con que se debe alimentar cada antena para aplicar los desfasajes correspondientes o en su defecto, calcular las fases para cada antena en una PC, mediante software y transmitirlo mediante protocolo serie RS232 o algún método alternativo, que permita variar la dirección del haz de radiación en tiempo real.

## VII. REFERENCIAS

- R. Gastaldi, J. Fernández, G. Caballero, J. Galleguillo, M. Busnardo, and S. Medina, "Desarrollo e implementación de sintesis de patrones de radiación sobre plataforma FPGA," UEA2011, Agosto 2011.

- [2] A. Natarajan, A. Komijani, and A. Hajimiri, "A fully integrated 24- GHz phased-array transmitter in CMOS," *Solid-State Circuits, IEEE Journal of*, vol. 40, no. 12, pp. 2502 2514, dec. 2005.

- [3] D. Parker and D. Zimmermann, "Phased arrays-part ii: implementations, applications, and future trends," Microwave Theory and Techniques, IEEE Transactions on, vol. 50, no. 3, pp. 688 –698, mar 2002.

- [4] J. Fernández, P. Sonna, G. Caballero, R. Gastaldi, M. Busnardo J. Galleguillo and S. Medina, "Implementación en FPGA de un Transmisor QPSK para un Conformador de Haz," UEA2012, Septiembre 2012.