#### INSTITUTO UNIVERSITARIO AERONÁUTICO

Faculta de Ingeniería

# Diseño e implementación de circuito impreso multicapa dedicado para sistema de control embebido basado en plataforma CIAA.

Por: Juan José Julca Yaya

Director: Ing. Javier Fernández

# "Diseño e implementación de circuito impreso multicapa dedicado para sistema de control embebido basado en plataforma CIAA."

Por

Juan José Julca Yaya

#### Resumen

Se diseña e implementa un circuito impreso de cuatro capas para un sistema de control embebido, aplicando reglas de diseño orientadas a preservar la compatibilidad electromagnética del mismo. Luego, mediante simulación del diseño en software especializado, se tratará de predecir el comportamiento del circuito.

Córdoba, 15 de diciembre de 2016

# **Contenidos**

| 1 | Intro | oduccion                                                 | 1  |

|---|-------|----------------------------------------------------------|----|

| 2 | Mar   | co Teórico                                               | 3  |

|   | 2.1.  | Circuitos Impresos                                       | 3  |

|   |       | 2.1.1. Software de diseño                                | 4  |

|   |       | 2.1.2. Esquemáticos                                      | 4  |

|   |       | 2.1.3. Huella                                            | 5  |

|   |       | 2.1.4. Editor de Esquemático                             | 6  |

|   |       | 2.1.5. Editor de PCB                                     | 7  |

|   | 2.2.  | Interferencia Electromagnética                           | 7  |

|   |       | 2.2.1. Compatibilidad Electromagnética                   | 7  |

|   |       | 2.2.2. Regulaciones de EMC                               | 8  |

|   | 2.3.  | Radiaciones de Circuitos Digitales                       | 9  |

|   |       | 2.3.1. Modo Diferencial                                  | 9  |

|   |       | 2.3.2. Modo Común                                        | 10 |

|   | 2.4.  | Comportamiento de componentes pasivos en radiofrecuencia | 10 |

|   |       | 2.4.1. Pistas de cobre                                   | 12 |

|   |       | 2.4.2. Capacitores                                       | 13 |

|   |       | 2.4.3. Factor de disipación                              | 15 |

|   |       | 2.4.4. Capacitores en paralelo                           | 15 |

|   |       | 2.4.5. Inductores                                        | 17 |

|   |       | 2.4.6. Chips de ferrite                                  | 18 |

| 3 | Dise  | eño del esquemático del PCB                              |    |

|   |       | •                                                        | 21 |

|   | 3.1.  | PCB basado en plataforma CIAA                            | 21 |

|   |       | Biblioteca de componentes                                |    |

|   |       | División del esquemático                                 |    |

|   |       | Esquemático Principal                                    |    |

#### CONTENIDOS Página III

|   |      | 3.4.1. Circuito Oscilador                                            |

|---|------|----------------------------------------------------------------------|

|   |      | 3.4.2. Botón de Reset                                                |

|   |      | 3.4.3. Conversores analógico-digitales                               |

|   |      | 3.4.4. Conversor digital-analógico                                   |

|   |      | 3.4.5. Salidas de alimentación                                       |

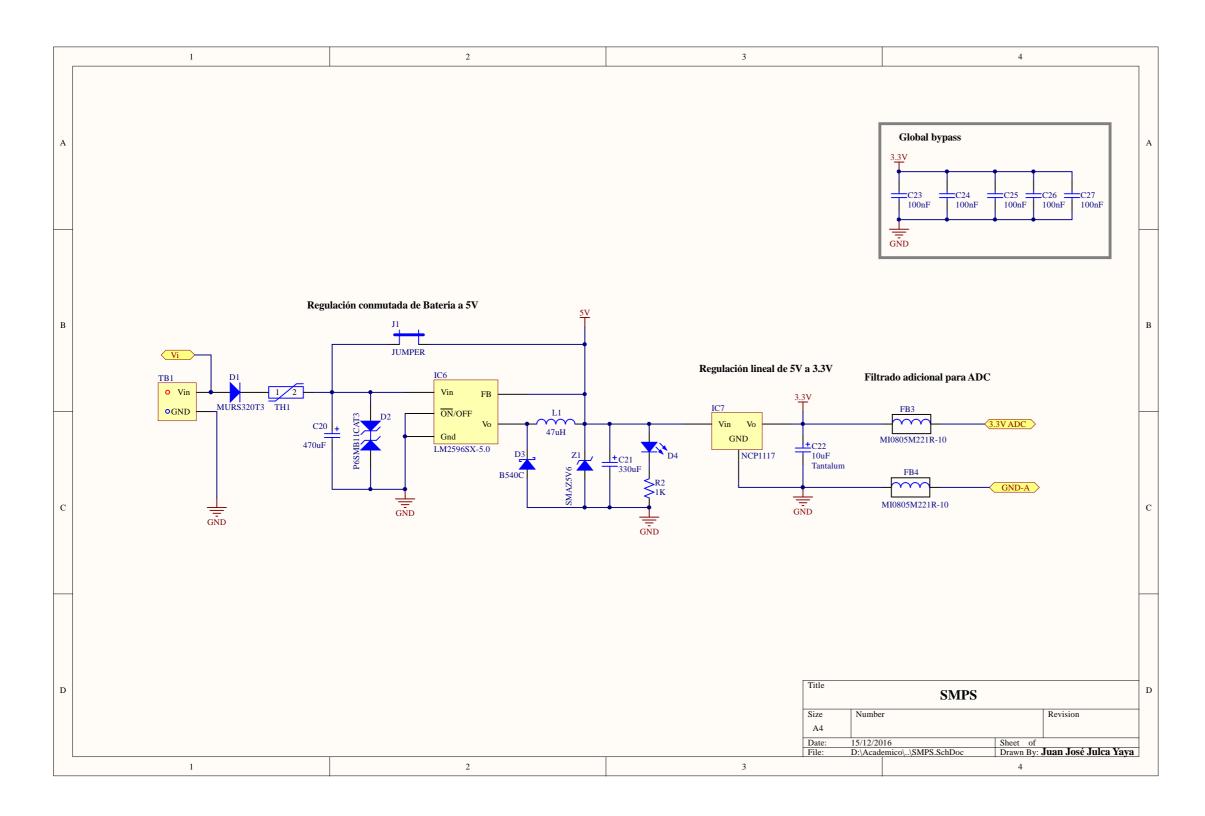

|   | 3.5. | Fuente Conmutada                                                     |

|   |      | 3.5.1. Filtro LC                                                     |

|   |      | 3.5.2. Diodo de freewheeling                                         |

|   |      | 3.5.3. Capacitor de entrada                                          |

|   |      | 3.5.4. Otras consideraciones                                         |

|   |      | 3.5.5. Ripple a la salida                                            |

|   | 3.6. | Fuente Lineal                                                        |

|   | 3.7. | PWR/GND                                                              |

|   |      | 3.7.1. Capacitor de desacoplo                                        |

|   | 3.8. | GPIO                                                                 |

|   |      | 3.8.1. Interruptores de entrada                                      |

|   | 3.9. | Dispositivos I2C                                                     |

|   |      | 3.9.1. Resistencias de pull up                                       |

|   | 3.10 | .Dispositivos varios                                                 |

|   |      | 3.10.1.LEDs indicadores                                              |

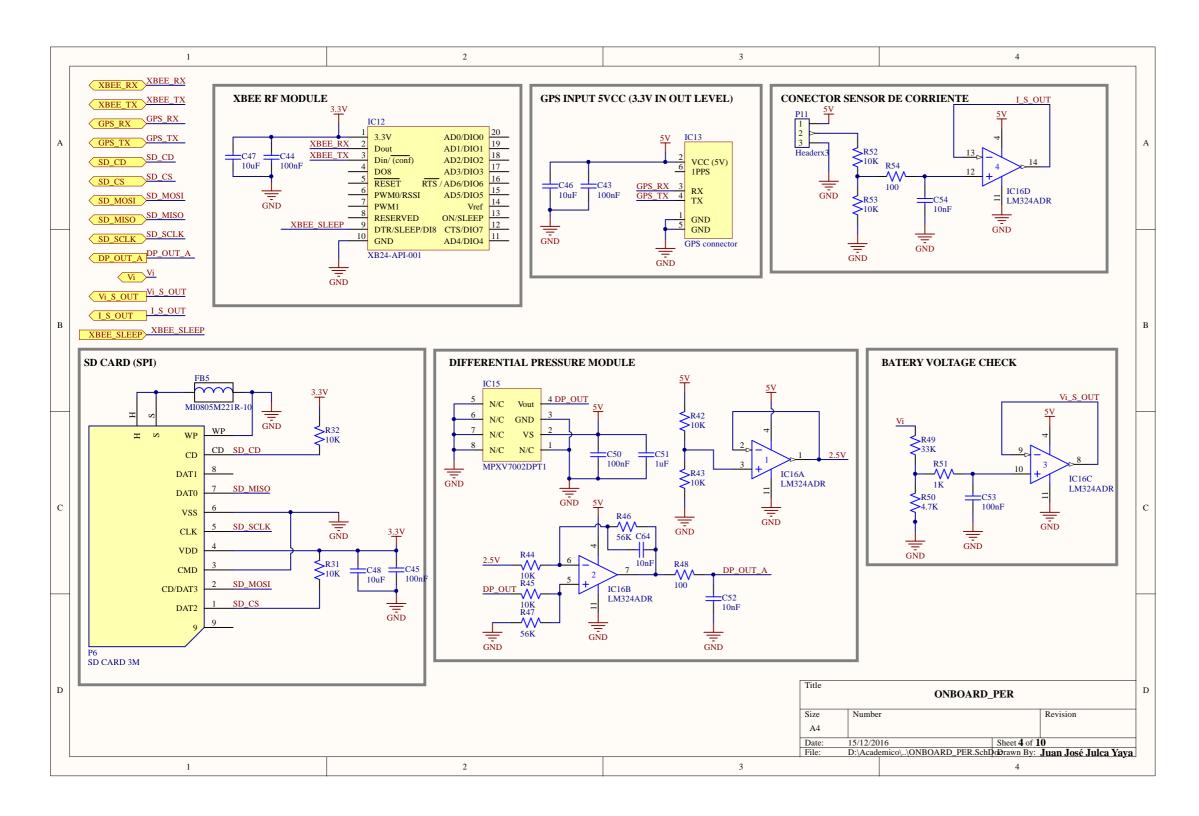

|   |      | 3.10.2.Módulo XBee                                                   |

|   |      | 3.10.3.Módulo GPS                                                    |

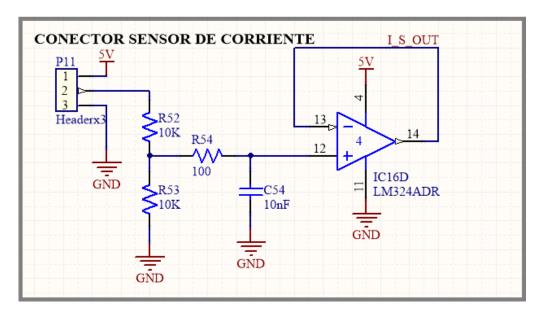

|   |      | 3.10.4. Sensor de Corriente                                          |

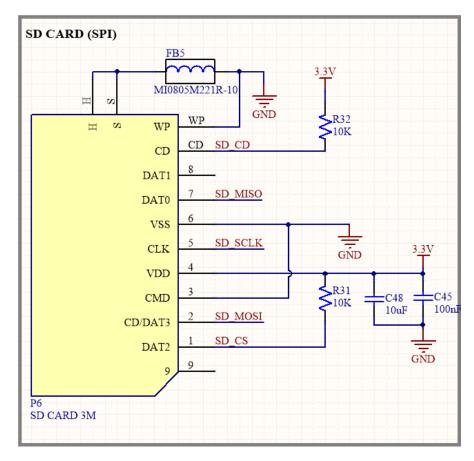

|   |      | 3.10.5. Memoria SD                                                   |

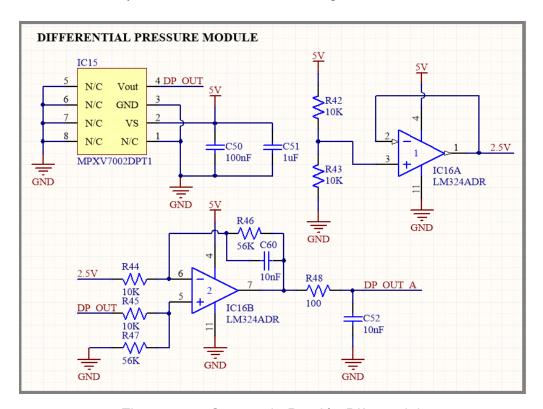

|   |      | 3.10.6. Sensor de presión diferencial                                |

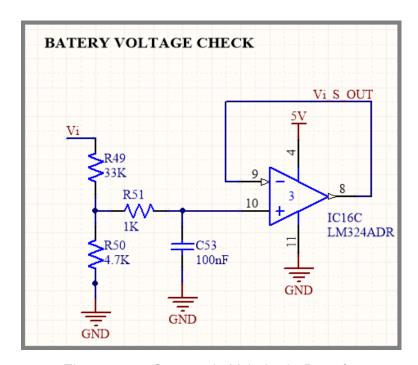

|   |      | 3.10.7. Sensor de voltaje de batería                                 |

|   | 3.11 | .Debugger                                                            |

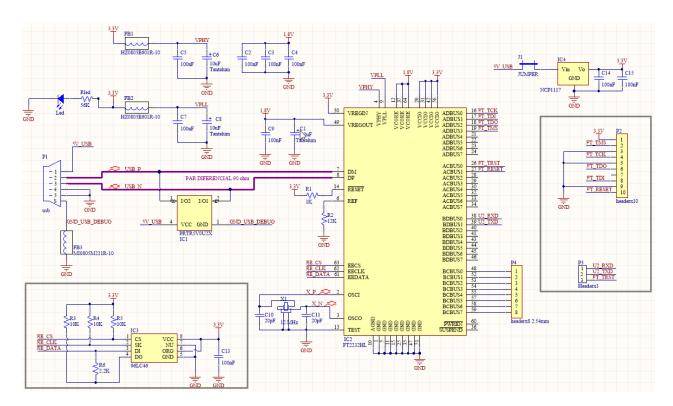

|   | 3.12 | .Diseño de un Debugger basado en FT2232H                             |

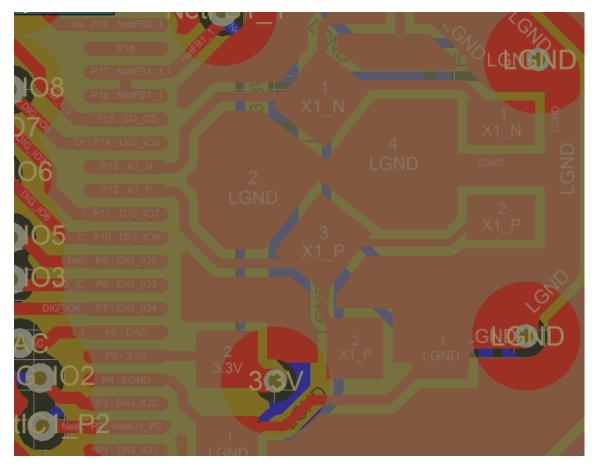

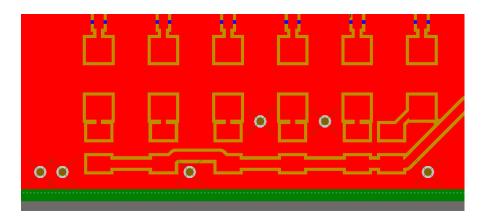

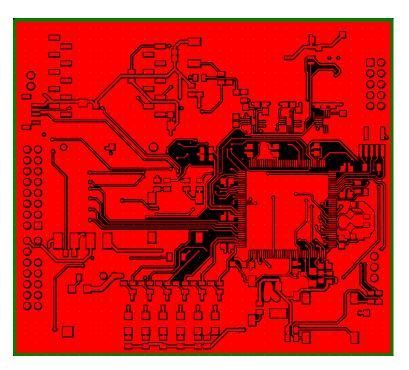

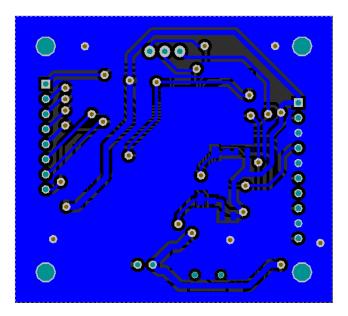

| 4 | Dise | eño de PCB de 4 capas 59                                             |

|   |      | Esquemático a PCB                                                    |

|   |      | Biblioteca de Huellas                                                |

|   |      | Stack Up                                                             |

|   |      | Reglas de Diseño                                                     |

|   |      | 4.4.1. Reducción de loops de GND 61                                  |

|   |      | 4.4.2. Caminos de baja inductacia para señales de alta frecuencia 65 |

|   |      | 4.4.3. Crosstalk                                                     |

|   |      |                                                                      |

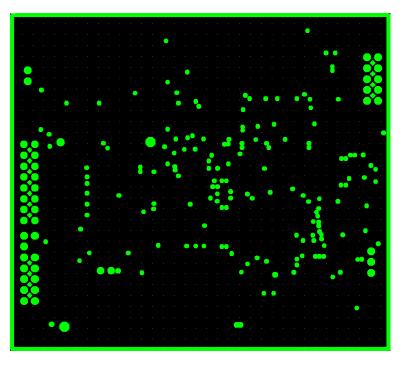

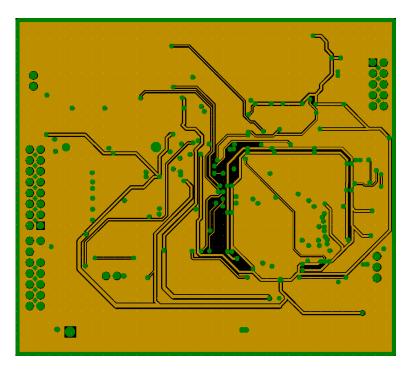

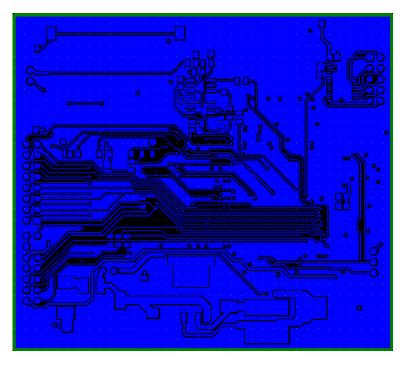

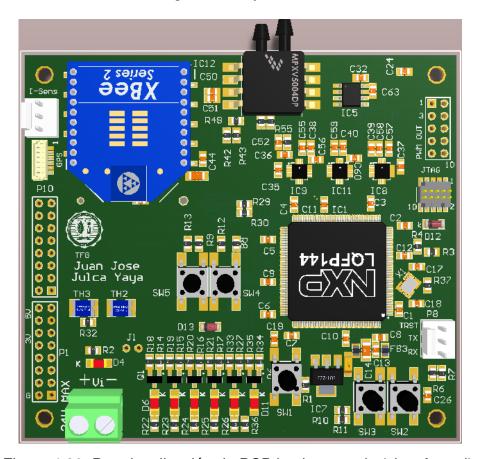

#### Simulación de PCB diseñado 83 83 Implementación 89 Diseño de PCB de 2 capas para Debugger 91

Conclusiones y trabajos futuros

Anexo B Simulación con 20 inversores

Anexo A Esquemáticos

Bibliografía

**CONTENIDOS**

Página IV

95

97

107

109

# Índice de figuras

| 2.1.  | Esquemático de conector de memoria SD                                               | 5   |

|-------|-------------------------------------------------------------------------------------|-----|

| 2.2.  | Huella del conector de memoria SD                                                   | 6   |

| 2.3.  | Tensión V usando el cable como antena.                                              | 11  |

| 2.4.  | Irradiación en modo común                                                           | 11  |

| 2.5.  | Dimensiones de pista que definen inductancia                                        | 12  |

| 2.6.  | Modelo que aproxima un capacitor real                                               | 13  |

| 2.7.  | Respuesta frecuencia-impedancia de un capacitor cerámico                            | 14  |

| 2.8.  | Curvas frecuencia vs. impedancia correspondientes a $C_{CER},C_{TANT}$ y $C_{PAR}.$ | 16  |

| 2.9.  | Modelo de un inductor real                                                          | 17  |

| 2.10. | .Respuesta frecuencia-impedancia                                                    | 18  |

| 2.11. | .Modelo de un chip de ferrite.                                                      | 19  |

| 2.12. | .Curva frecuencia vs. impedancia correspondiente a un chip de ferrite               | 20  |

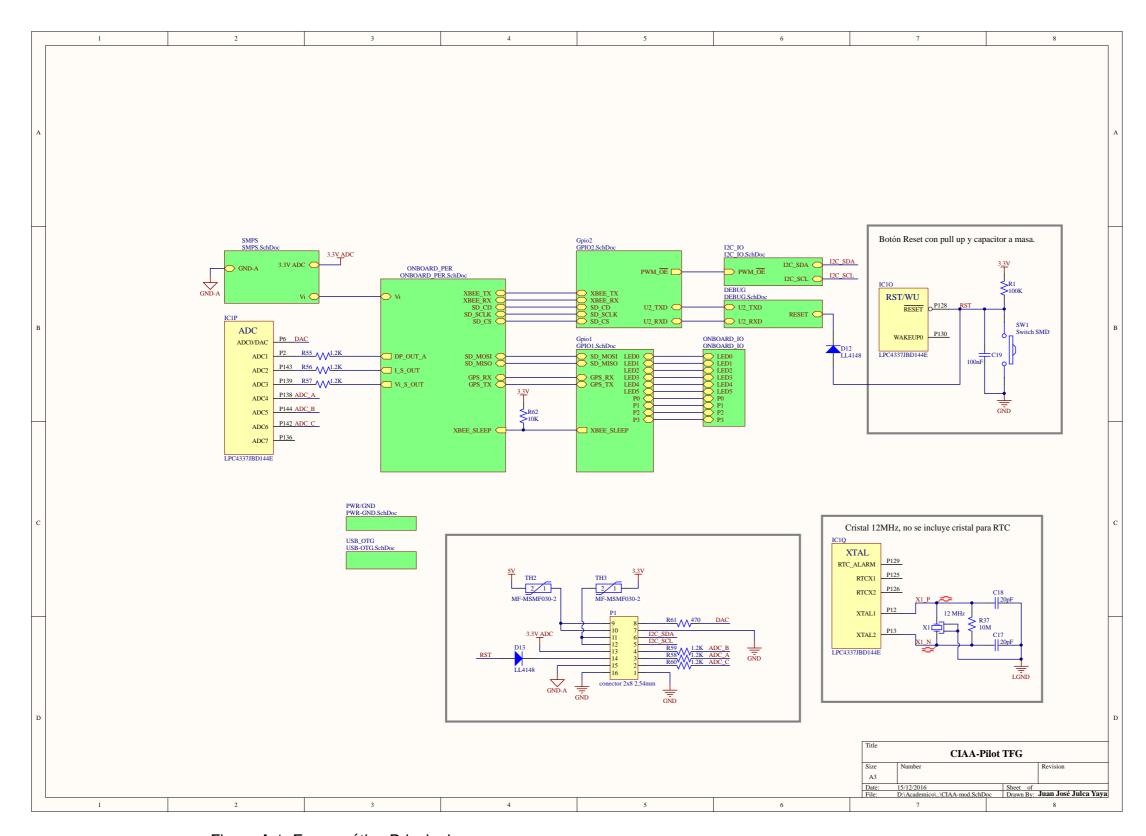

| 3.1.  | Estructura del esquemático                                                          | 23  |

| 3.2.  | Circuito del oscilador Pierce                                                       | 23  |

| 3.3.  | Circuito del botón de reset                                                         | 24  |

| 3.4.  | Circuito de simulación del botón reset                                              | 25  |

| 3.5.  | Resultado de la simulación del botón reset                                          | 26  |

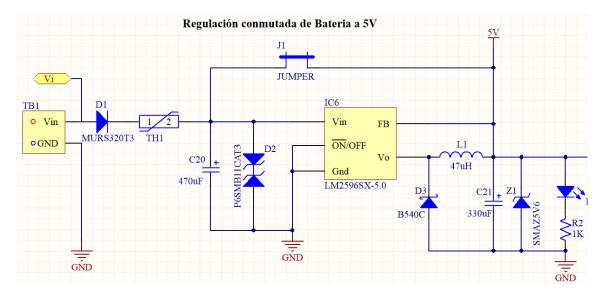

| 3.6.  | Circuito de la fuente conmutada                                                     | 27  |

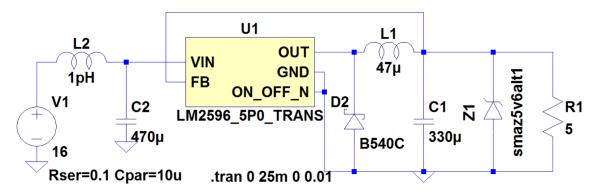

| 3.7.  | Circuito de simulación SMPS                                                         | 30  |

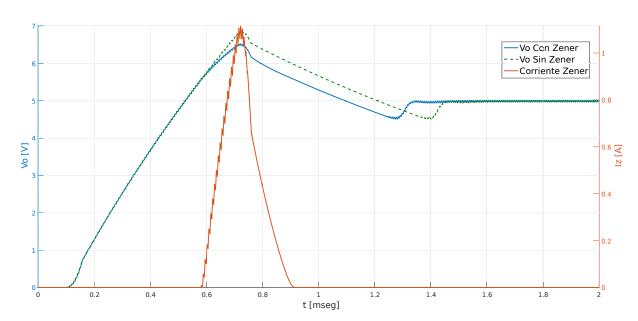

|       | (izquierda) tiempo vs. voltaje de salida (derecha) tiempo vs. corriente del Zener   | 0.0 |

|       | para RL= $5 \Omega$                                                                 | 30  |

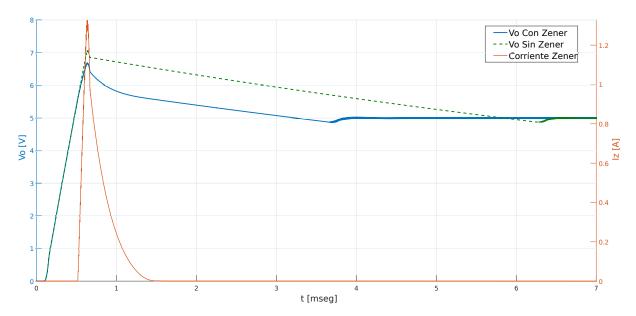

|       | (izquierda) tiempo vs. voltaje de salida (derecha) tiempo vs. corriente del Zener   |     |

|       | para RL= $50~\Omega$ .                                                              |     |

|       | . Ripple de voltaje para tres corrientes cuando la entrada es $V_{in}=16~V.$        |     |

|       | .Ripple de voltaje para tres corrientes cuando la entrada es $V_{in}=24~V$          |     |

|       | .Regulador lineal con salida $3.3\ V$ y filtrado con ferrites                       |     |

|       | Esquema de simulación de la fuente lineal con ruido inyectado                       |     |

| 3 14  | Respuesta del regulador lineal                                                      | 34  |

#### Índice de figuras

| Pág | ina | ۷I |

|-----|-----|----|

|     |     |    |

| 3.15. Ampliación de figura 3.14 en estado de regimen.                                     | 35 |

|-------------------------------------------------------------------------------------------|----|

| 3.16. Inversor con transistores de $0.35~\mu m$ de ancho de canal                         | 36 |

| 3.17. Circuito de simulación con inversor                                                 | 37 |

| 3.18.Resultados de la simulación del inversor.                                            | 37 |

| 3.19. Fuente ideal afectada por conmutaciones del inversor                                | 38 |

| 3.20. Fuente ideal afectada por 60 inversores                                             | 38 |

| 3.21. Alimentación con capacitor de desacoplo Ideal, Tantalio y Cerámico                  | 40 |

| 3.22. Simulación con 20 inversores a $10~MHz$ y tiempo de crecimiento $10~ns.$            | 42 |

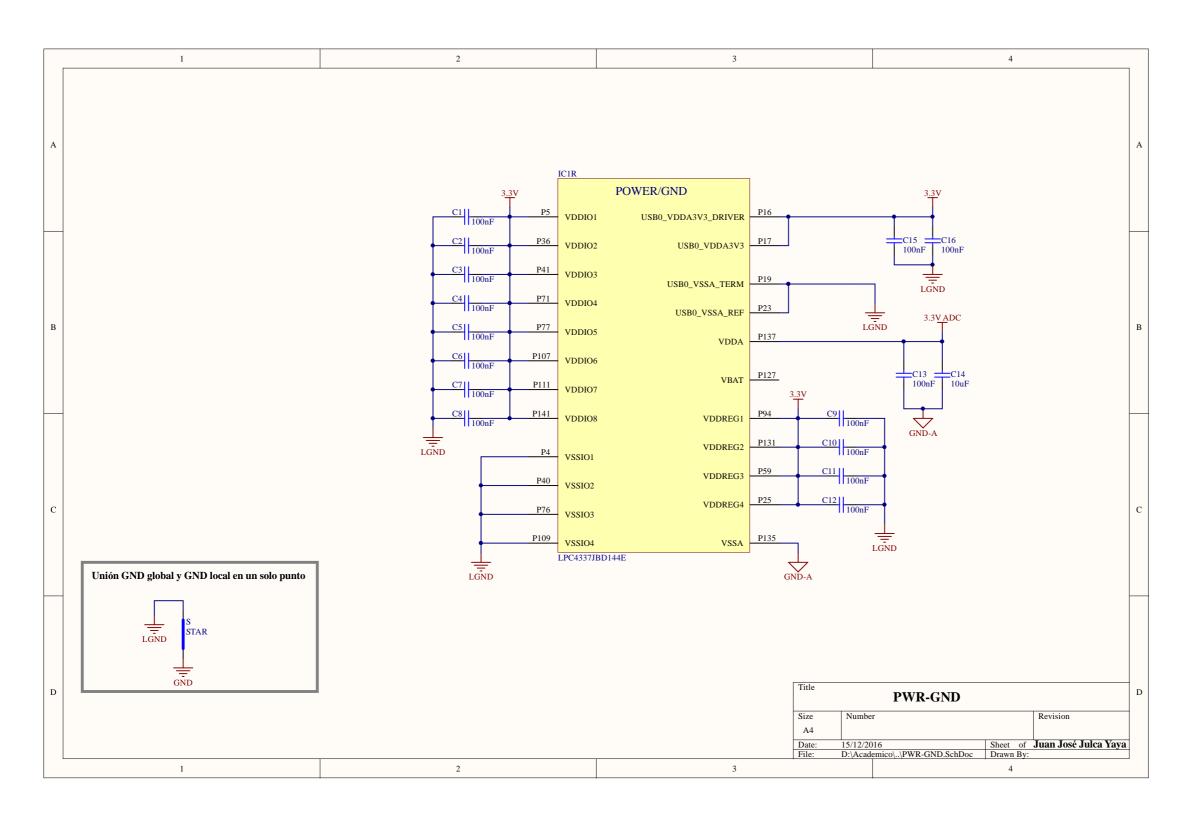

| 3.23. Esquemático de alimentación del microcontrolador NXP LPC4337                        | 43 |

| 3.24. Esquemático de interruptores                                                        | 44 |

| 3.25. Esquemático de conexión del bus $I^2C$ del microcontrolador                         | 46 |

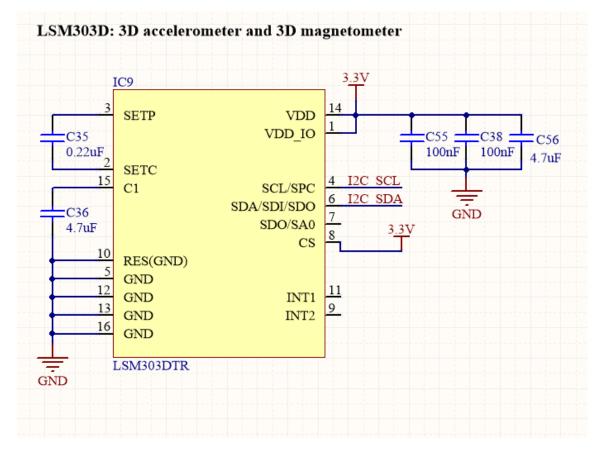

| 3.26.Esquemático del LSM303D                                                              | 47 |

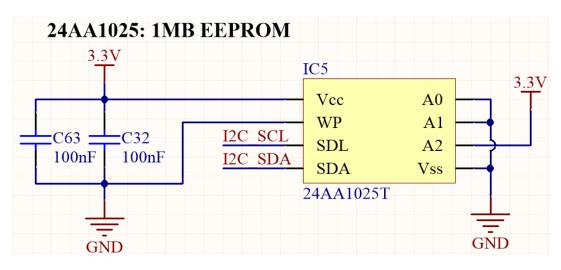

| 3.27.Esquemático del 24AA1025                                                             | 48 |

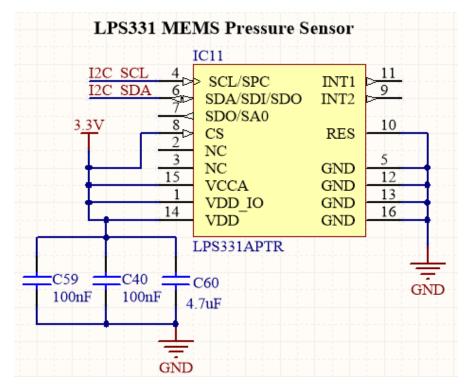

| 3.28.Esquemático del LPS331                                                               | 48 |

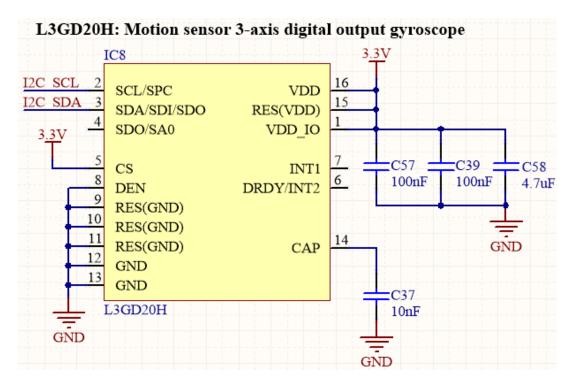

| 3.29.Esquemático del L3GD20H                                                              | 49 |

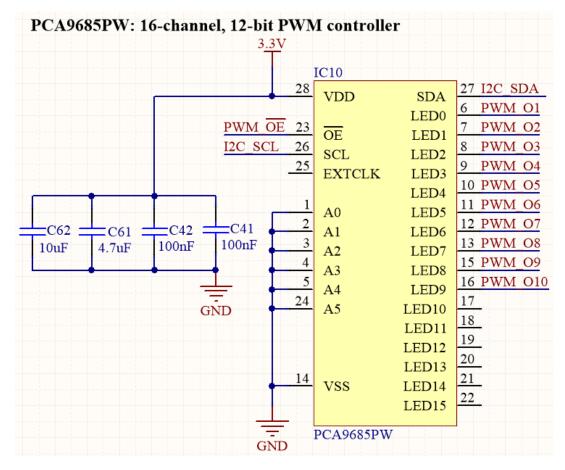

| 3.30.Esquemático del PC9685PW                                                             | 49 |

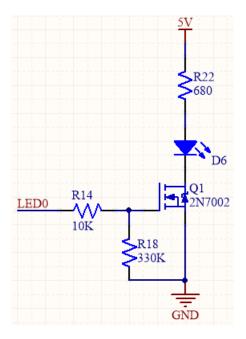

| 3.31.Esquemático de Leds indicadores                                                      | 50 |

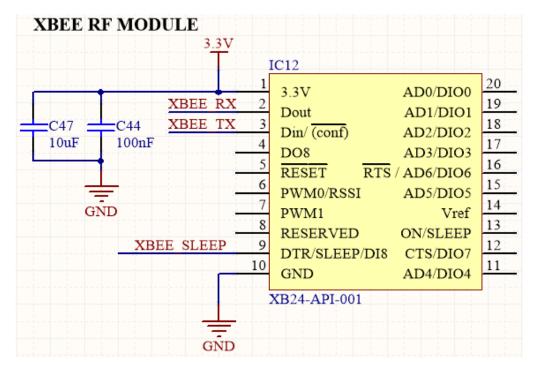

| 3.32.Esquemático XBEE XB24-API-001                                                        | 51 |

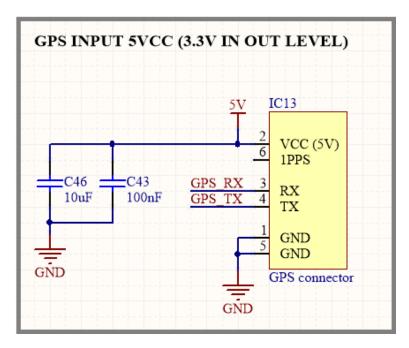

| 3.33.Esquemático GPS EM 506                                                               | 52 |

| 3.34. Sensor de Corriente                                                                 | 53 |

| 3.35.Memoria SD                                                                           | 53 |

| 3.36.Sensor de Presión Diferencial                                                        | 54 |

| 3.37.Sensor de Voltaje de Batería                                                         | 55 |

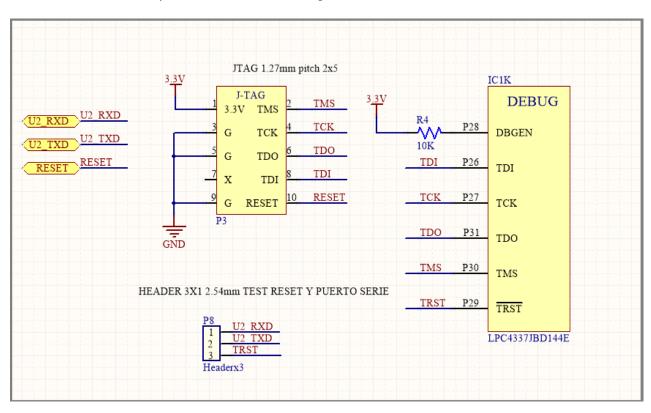

| 3.38.Esquemático del puerto de Debug                                                      | 56 |

| 3.39.Esquemático del debugger externo                                                     | 57 |

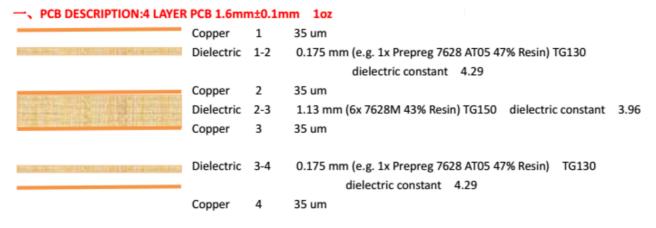

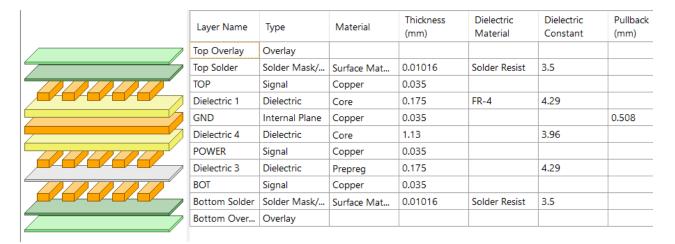

| 4.1. Stack Up del fabricante                                                              | er |

| 4.2. Stack Up en Altium.                                                                  |    |

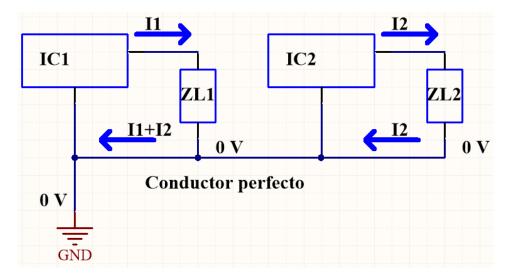

| 4.3. Conexión con plano de masa perfecto                                                  |    |

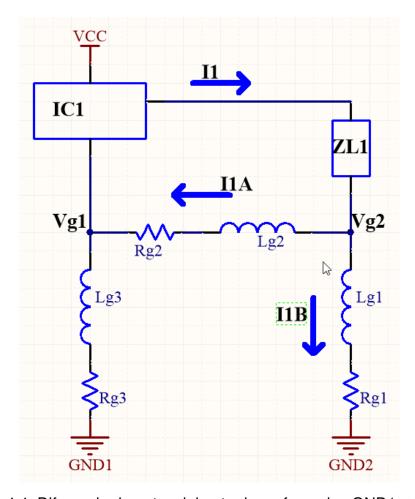

| 4.4. Diferencia de potencial entre las referencias GND1 y GND2                            |    |

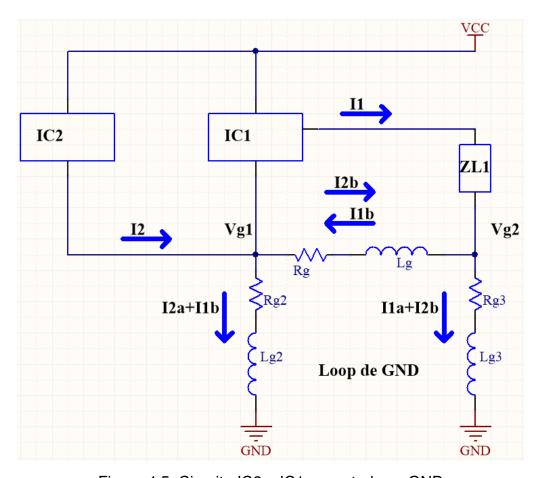

| 4.5. Circuito IC2 e IC1 conectados a GND                                                  |    |

| 4.6. Esquemático anexo al de la figura 3.36.                                              |    |

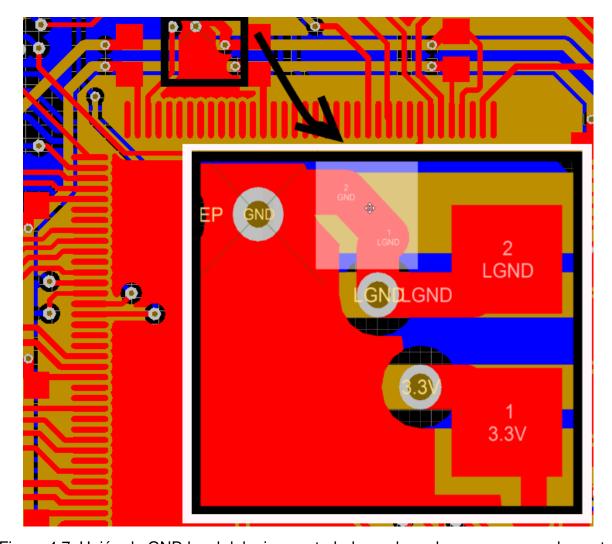

| 4.7. Unión de GND local del microcontrolador a plano de masa en un solo punto             |    |

| 4.8. Distribución de corriente de retorno                                                 |    |

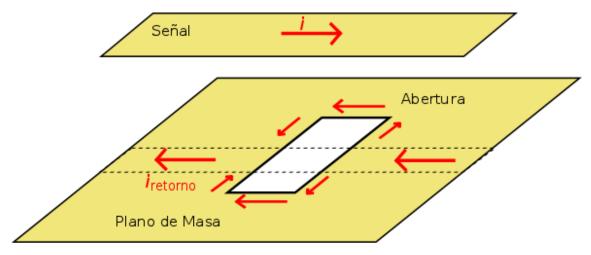

| 4.9. Abertura en el plano de masa debajo de una pista portadora de señal                  |    |

| 4.10. Plano de masa continuo sobre las pistas de alta frecuencia del oscilador a cristal. |    |

| 4.11.CTC                                                                                  |    |

| T.I I.O I O                                                                               | UC |

#### Índice de figuras Página VII

| _    | 1011         |             |         | ĺ | Índi | се | de | fig | jur | as |  |  |  |  |  |  | Pá | ági | ina | a VIII |

|------|--------------|-------------|---------|---|------|----|----|-----|-----|----|--|--|--|--|--|--|----|-----|-----|--------|

| A.2. | PWR-GND.     |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 99     |

|      | Fuente Con   |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     |        |

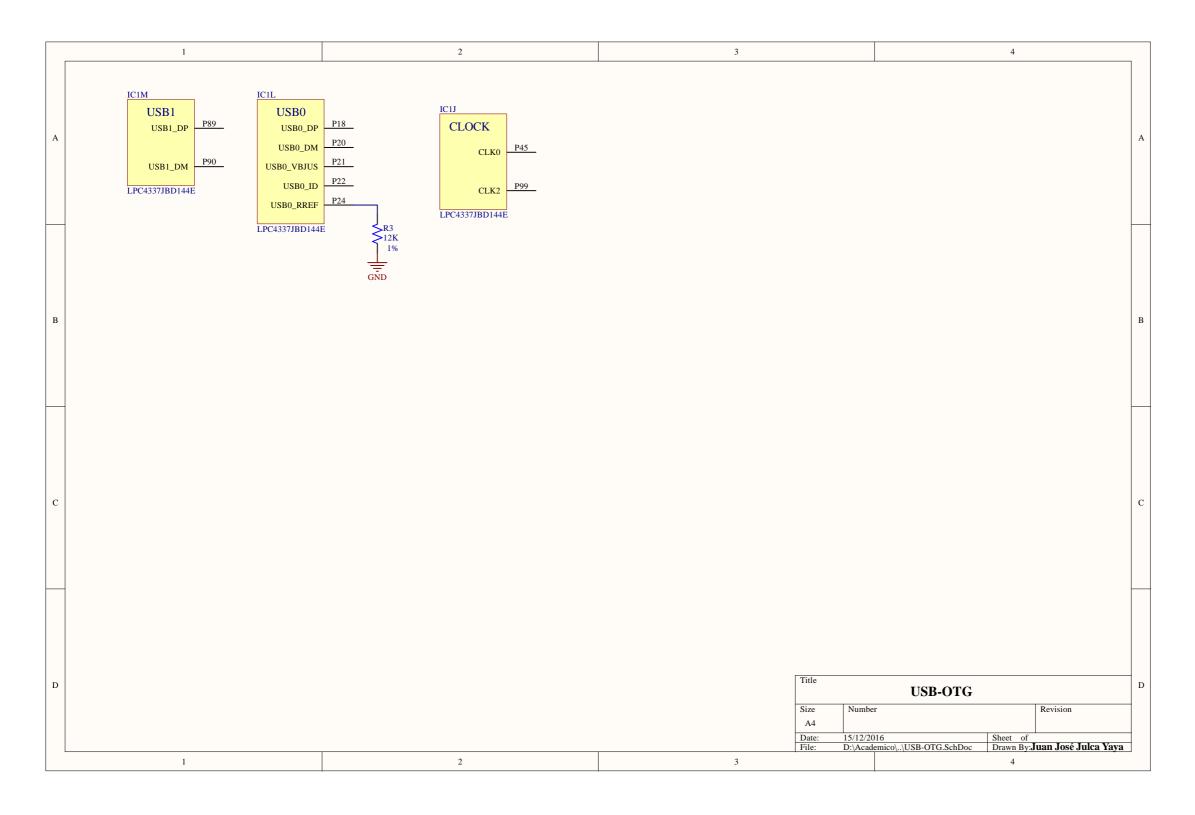

| A.4. | USB-OTG.     |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 101    |

| A.5. | ONBOARD      | PERIPHE     | RALS.   |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 102    |

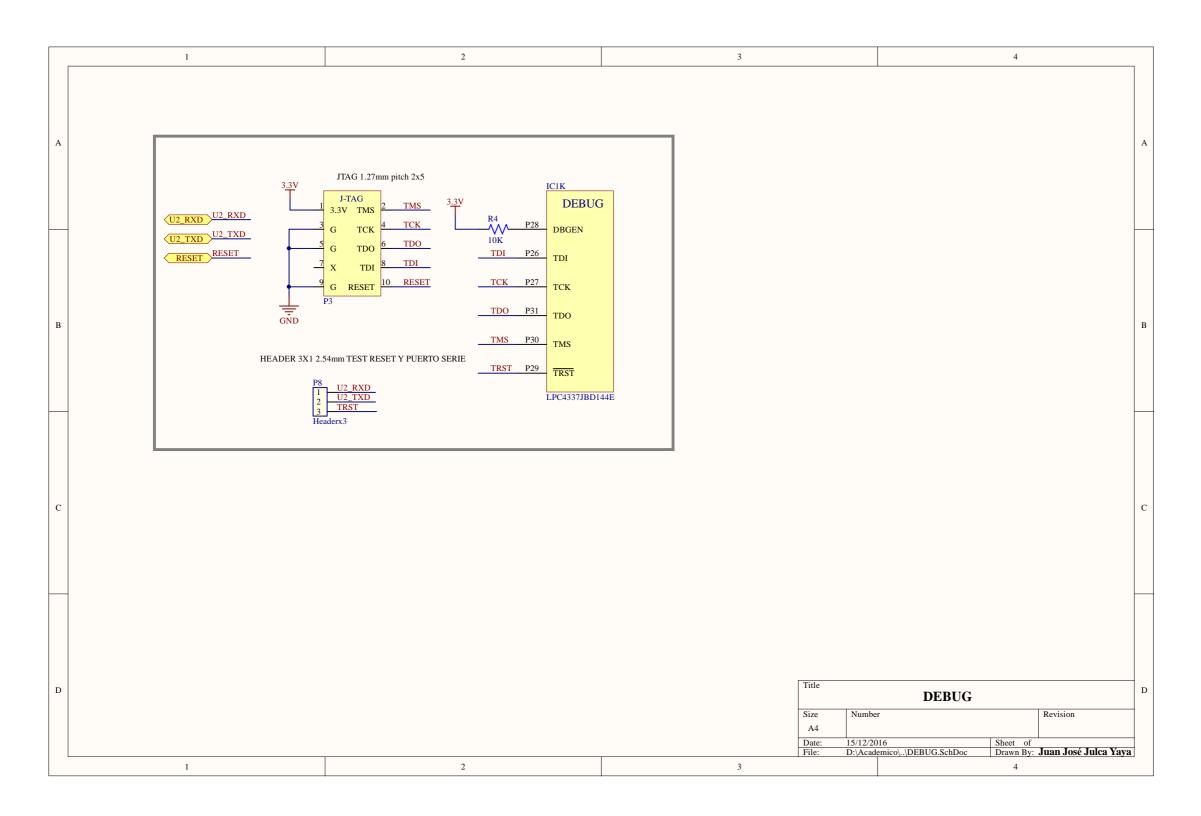

| A.6. | DEBUG        |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 103    |

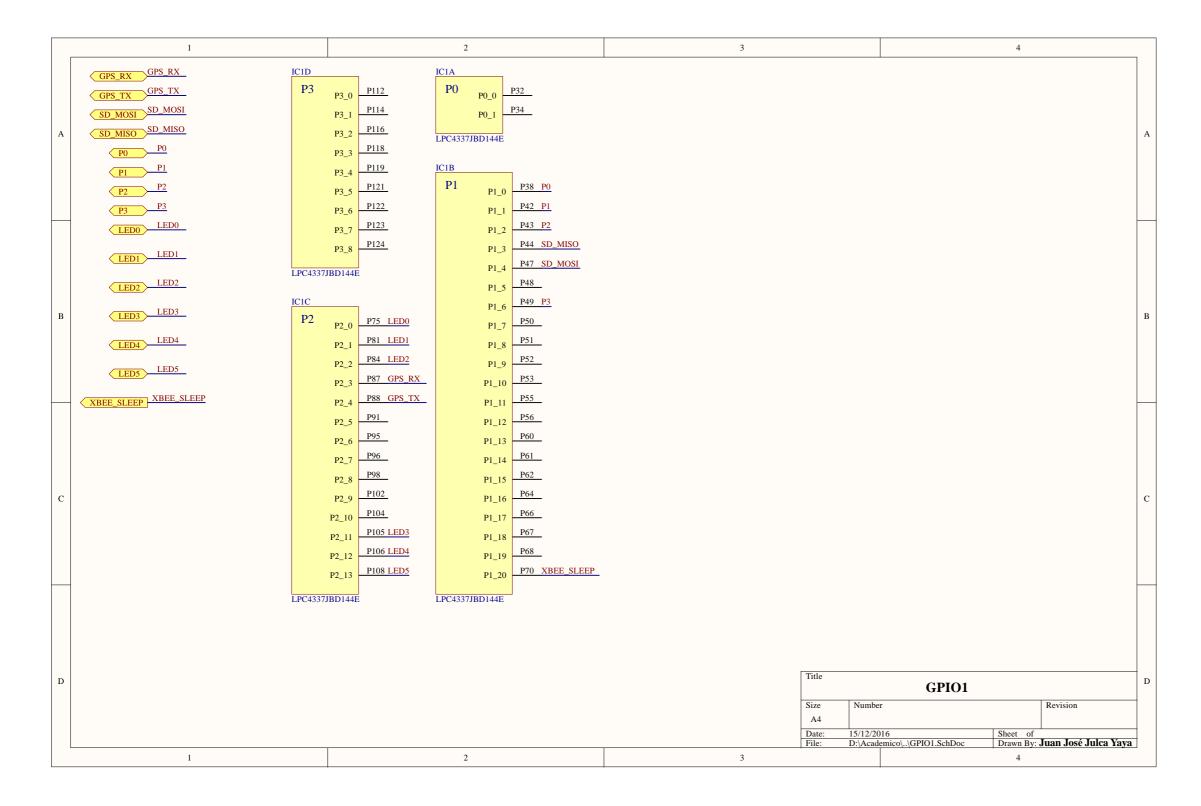

| A.7. | GPIO I       |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 104    |

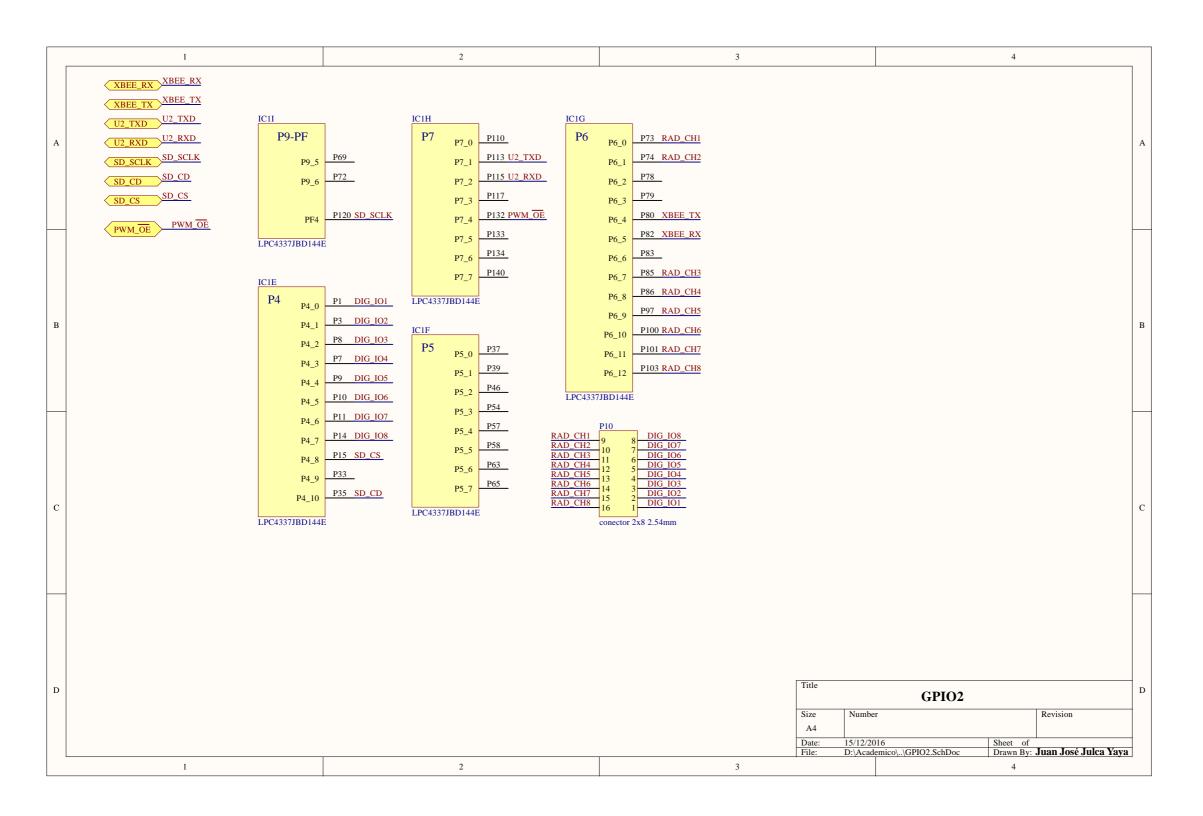

| A.8. | GPIO II      |             |         |   |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 105    |

| B.1. | Simulación o | con 20 inve | ersores | S |      |    |    |     |     |    |  |  |  |  |  |  |    |     |     | 108    |

# Índice de tablas

| 2.1. | Límites de raduación FCC a 3 m                                      | 9  |

|------|---------------------------------------------------------------------|----|

| 3.1. | Tabla de selección rápida de capacitor/inductor de filtro           | 28 |

| 3.2. | Inductacia equivalente en serie Capacitores Cerámicos y de Tantalio | 39 |

| 3.3. | Resistencia equivalente en serie de varios capacitores              | 40 |

| 3.4. | Especificaciones relevantes del bus $I^2C$                          | 46 |

| 4.1. | Resultado de CTI para método de separación de pistas                | 71 |

| 4.2. | Especificaciones de fabricación.                                    | 73 |

## Capítulo 1

#### Introducción

Todo sistema de control digital embebido requiere de sensores, actuadores y circuitos analógicos y digitales de acondicionamiento y control, donde cada uno de estos elementos se interconecta a través de conexiones eléctricas de un metal determinado en una placa que contiene todo el circuito. Esta placa se denomina «Placa de circuito impreso» (por sus siglas en inglés PCB «Printed circuit board»).

La forma en que se realiza las conexiones eléctricas en el PCB depende del diseñador y existen infinitas formas de realizarlas de tal forma que se respete el diagrama eléctrico del diseño (mapa de conexiones de cada parte del circuito). El criterio del diseñador para realizar esta tarea define, además del tamaño, facilidad de uso y estética, el grado de compatibilidad electromagnética del PCB.

Compatibilidad electromagnética (por sus siglas en inglés EMC «Electromagnetic compatibility»), como se verá más adelante, es un término que se refiere dos aspectos de cualquier dispositivo electrónico: Cuán susceptible es un equipo a ser afectado por campos electromagnéticos (CEM) externos, y a la medida en que es capaz este mismo equipo de afectar otros o a sí mismo.

En aplicaciones críticas, como un sistema de control de vuelo o un sistema médico de soporte de vida, el control de medidas de EMC no solo es importante, es mandatorio. Existen normas que establecen niveles máximos de radiación de cualquier PCB diseñado, como por ejemplo las reglas de la Federal Communications Commission (por sus siglas en inglés FCC).

Para lograr que el equipo que se desarrolla sea electromagnéticamente compatible, se recurre a un conjunto de reglas de diseño que afectan el grado de EMC. Estas reglas en gran parte de la bibliografía consultada son denominadas «Rules of thumb», frase que podría traducirse a «Reglas de oro» y son reglas que deberán ser analizadas para validar su aplicación durante el desarrollo de este trabajo.

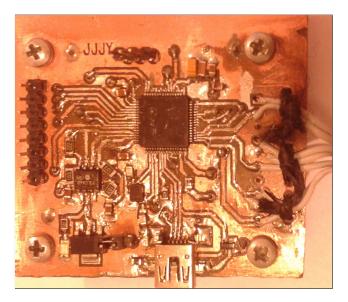

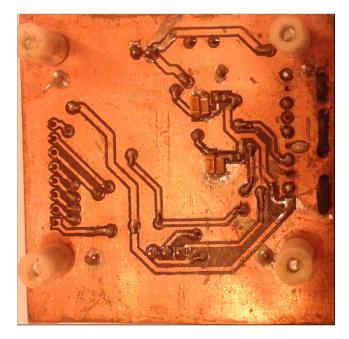

La aplicación de estas reglas se realizarán en el marco del diseño e implementación de

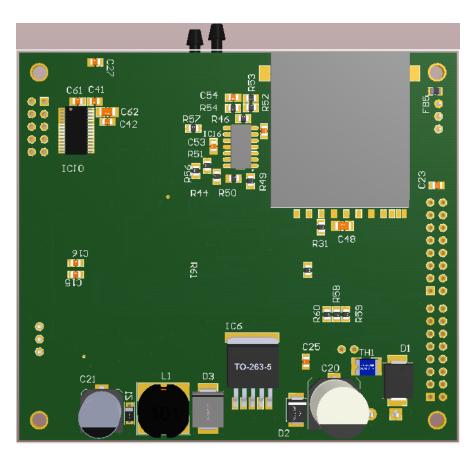

un PCB para un sistema de control embebido, el cual es un retrabajo de un prototipo funcional [1] realizado integrando módulos comerciales con conectores genéricos de  $2.54\ mm$  de espaciado en una placa de desarrollo EDU-CIAA [2], hacia un solo PCB de propósito específico.

En el capítulo 2 se presenta un marco teórico que plantea los conceptos más importantes que el autor considera importantes para el análisis y determinación de reglas de diseño aplicables al desarrollo del PCB.

En el capítulo 3 se detallan los lineamientos y cálculos de diseño del diagrama eléctrico del PCB. El capítulo 4 muestra como las reglas seleccionadas son aplicadas a la realización del PCB mediante el uso de software especializado.

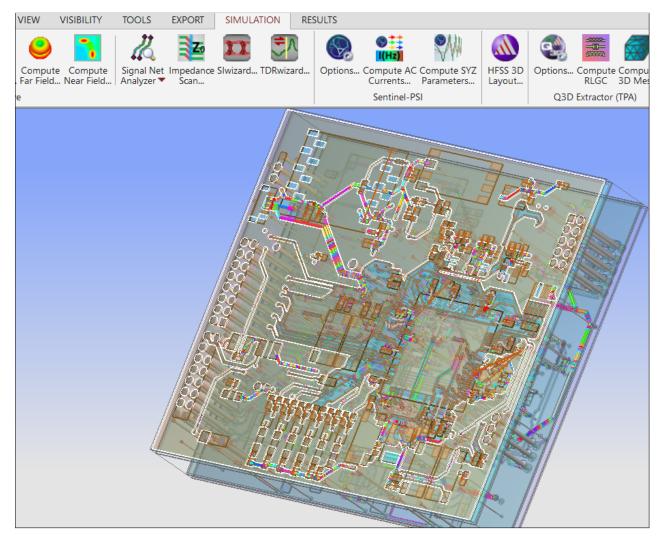

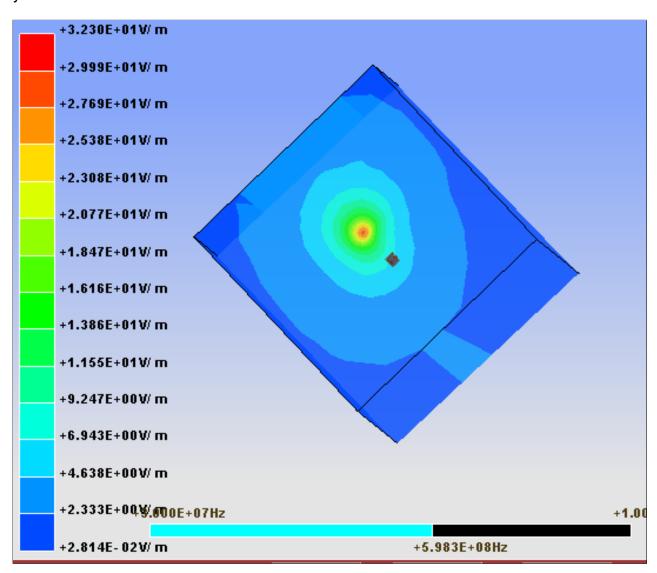

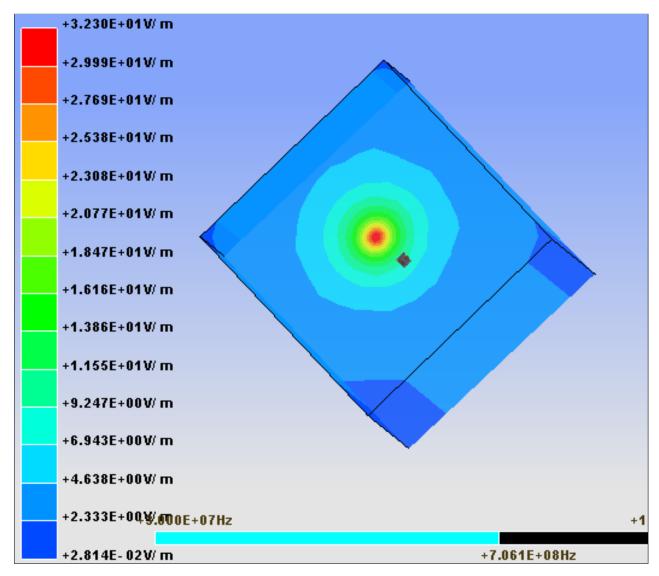

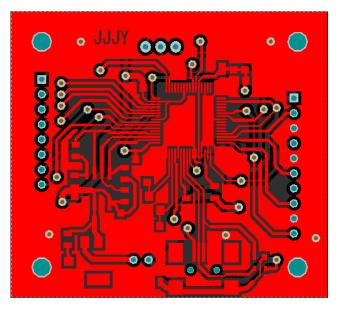

En el capítulo 5 se muestra el procedimiento de simulación del campo electromagnético irradiado del PCB diseñado, luego, en el capítulo 6 se mostrará la implementación y una prueba funcional básica. Finalmente en el capítulo 8 se detallan las conclusiones del trabajo realizado y el planteamiento de trabajos futuros de acuerdo a la experiencia adquirida.

## Capítulo 2

#### **Marco Teórico**

En este capítulo se desarrollan conceptos que se usarán durante el desarrollo del presente trabajo.

#### 2.1. Circuitos Impresos

Un circuito impreso o PCB (del inglés, Printed Cicuit Board) <sup>1</sup> es una placa que consta de dos partes:

- Plano conductor.

- Dieléctrico de separación.

El plano conductor es una superficie de material conductor (generalmente y específicamente en este trabajo, cobre). Esta capa de cobre tiene un grosor determinado y su fabricación procura que este grosor sea constante en toda la superficie.

La forma en que los fabricantes detallan el grosor de la capa de cobre es dando información de volumen de cobre por superficie, en general las unidades que se usan son unidades del sistema imperial: Onzas por pulgada cuadrada  $(oz/in^2)$ .

Por ejemplo, la placa que se utilizó posee cuatro capas de cobre de  $1\ oz/in^2$ , si se considera que la densidad del cobre es de  $8950\ kg/m^3$ , se llega a que el grosor de cada capa es de  $0.035\ mm$ .

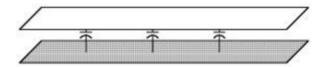

Cada capa de cobre es separada por material dieléctrico que aísla eléctricamente las capas de cobre contiguas una de la otra. Una placa de 4 capas (de cobre) posee 3 planos dieléctricos cuyo grosor es determinado por el fabricante.

<sup>&</sup>lt;sup>1</sup> Ambos términos serán usados indistintamente durante el desarrollo del trabajo.

La configuración de grosor de capas de cobre y dieléctrico (número y grosor de cada una) es llamada «Stack Up». En la capa de cobre se crearán los caminos eléctricos y las terminales de soldado (del inglés «Pad») que definen la funcionalidad del PCB.

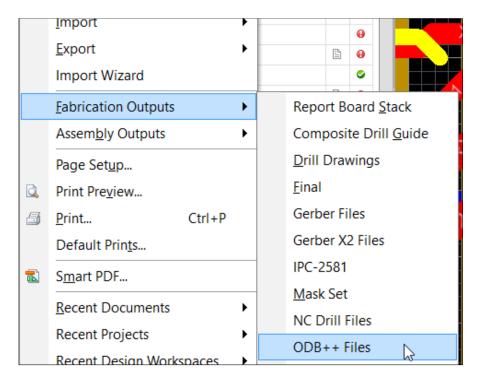

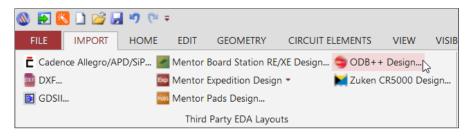

#### 2.1.1. Software de diseño

La herramienta de diseño del PCB define la terminología y el tipo de archivos de exportación para el uso de otros programas para el análisis de compatibilidad electromagnética de este trabajo.

Existen varias herramientas como Eagle, KiCAD, Altium Designer, Cadence Allegro, etc., todas bajo la denominación software CAD (del inglés Computer-Aided Design). Por ejemplo, la plataforma EDU-CIAA, fue diseñada usando KiCAD, el cual es el único software de distribución libre de los mencionados.

Para este trabajo se empleó Altium Designer<sup>2</sup>, que es un software de uso generalizado en la industria de manufactura y diseño de PCB. Altium cuenta con tres herramientas principales para el desarrollo de un PCB: editor de esquemáticos, editor de PCB y gestor de biblioteca de esquemático y PCB.

#### 2.1.2. Esquemáticos

La palabra «esquemático» puede hacer referencia a cualquiera de 3 niveles de jerarquía en el desarrollo del PCB:

- Equemático general: Este indica el conexionado del circuito global, puede conectar sub-esquemáticos de los cuales solo son visibles sus puertos de entrada y salida, de esta forma se puede obtener una vista resumida de todo el diagrama del circuito. Este esquemático es de mucha utilidad para circuitos con gran cantidad de componentes (como el caso de este trabajo).

- Sub-esquemático: Es un diagrama de una sección específica, se puede tratar de una etapa de acondicionamiento de señal o una etapa de amplificación, describe de forma detallada el conexionado de cada componente.

- Esquemático de un componente: Cada componente tiene un número de patas o pines que deben ser conectadas de forma específica para lograr su funcionalidad, por ejemplo, el pin de alimentación, el pin de GND, el pin de salida de voltaje, etc. Por cada componente existe un esquemático asociado que le otorga a cada pin un designador y un nombre.

<sup>&</sup>lt;sup>2</sup>Se referirá a este software solamente como «Altium».

El designador se relaciona con la ubicación física de cada pin y el nombre indica por lo general la abreviación de la función que realiza el pin. Por ejemplo, el pin de realimentación de un integrado «IC1» puede tener el designador «5» y llevar el nombre «FB» que hace referencia a «feedback». «IC1-5» hace referencia al pin de realimentación de este integrado específico.

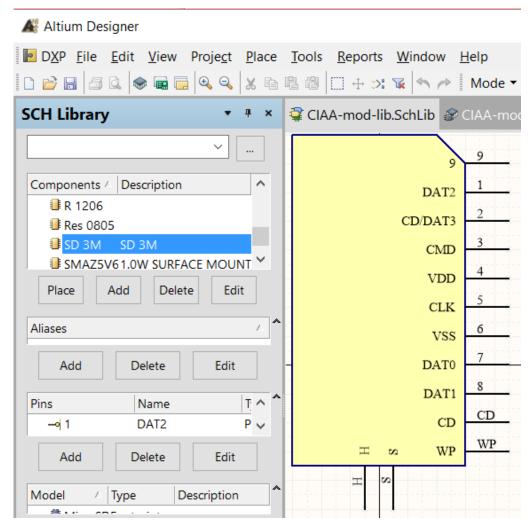

En la figura 2.1 se muestra un esquemático del conector de memoria SD 3M, donde se puede apreciar los designadores (fuera de polígono amarillo) y los nombres de cada pin (dentro de polígono amarillo).

Figura 2.1: Esquemático de conector de memoria SD.

#### 2.1.3. Huella

La huella de un componente o «Footprint» <sup>3</sup> se refiere al sector de cobre que requiere el componente para ser montado en una placa, esta define el tamaño de los pads de agujero

<sup>&</sup>lt;sup>3</sup>Ambos términos se emplearán indistintamente durante el desarrollo de este trabajo.

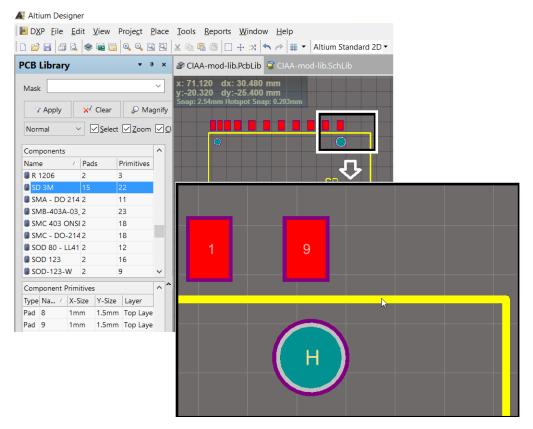

Figura 2.2: Huella del conector de memoria SD.

pasante definiendo el diámetro interno y externo o de SMD (del inglés Surface-Mount Device), definiendo las dimensiones y forma del pad.

En Altium cada huella está asociada a cada pin del esquemático de componente a través del designador. La huella correspondiente al esquemático mostrado en la figura 2.1, se presenta en la figura 2.2, se observa en la ampliación de la misma figura como los pads (color rojo) llevan como nombre el correspondiente designador del esquemático.

#### 2.1.4. Editor de Esquemático

El editor de esquemáticos de Altium permite diagramar el conexionado eléctrico de cada componente que se emplee en el diseño. El usuario debe crear líneas de conexión que servirán como guía para la distribución que se realiza en el editor de PCB.

Entre otras funciones, el editor puede generar un diagrama jerárquico en el que un solo esquemático general contiene varios subesquemáticos que tienen sus propias conexiones internas y crear puertos de voltaje y GND que son válidos en todos los esquemáticos.

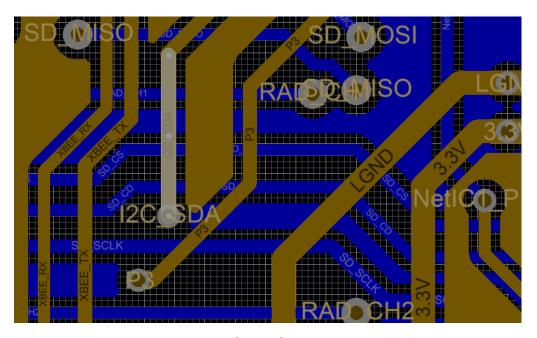

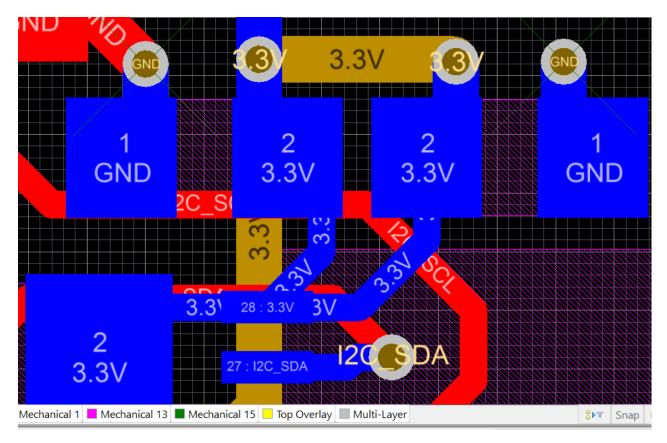

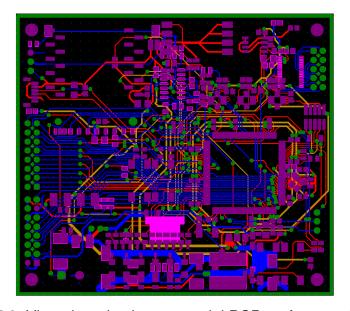

#### 2.1.5. Editor de PCB

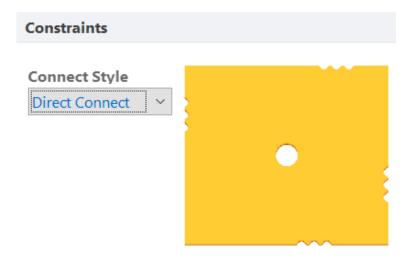

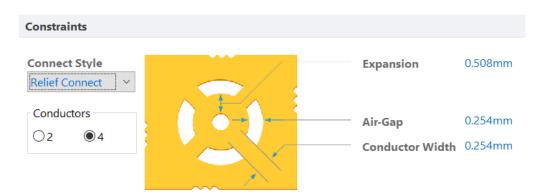

El editor de PCB es en donde se diseña el PCB en sí. De acuerdo a las conexiones creadas en el editor de esquemático, se crean conexiones llamadas «ratlines», que simplemente son líneas que unen los pads de cada componente en los nodos correspondientes en concordancia con el diagrama eléctrico<sup>4</sup>.

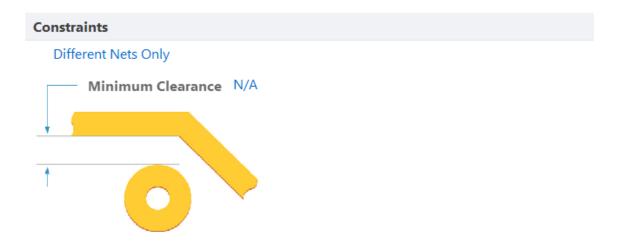

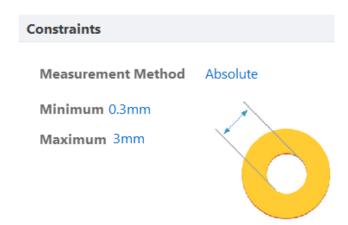

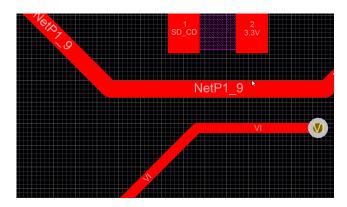

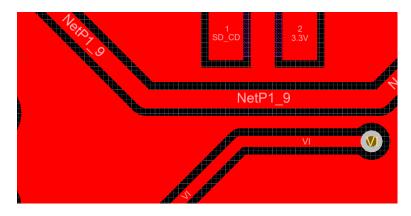

En el editor de PCB se deben configurar las reglas de diseño, como separación entre pistas, máximo ancho de pistas etc. Se crean los componentes a partir del esquemátido y con las reglas configuradas el diseñador debe elegir una distribución de todos estos y realizar las conexiones necesarias mediante una pista de cobre directa sobre la misma capa de cobre o usando vías.

#### 2.2. Interferencia Electromagnética

La interferencia electromagnética (por sus siglas en inglés, EMI) es el grado en que radiaciones de campo electromagnético de alguna fuente que afecta el funcionamiento de un circuito (víctima) y también el grado en que funcionamiento del circuito afecta a otros equipos (víctima vista como fuente).

En general, para cualquier dispositivo, se habla de tres formas de EMI:

- Interferencias causadas por otros al dispositivo.

- Interferencias que se causa el dispositivo a otros.

- Interferencias que el dispositivo se causa a sí mismo.

#### 2.2.1. Compatibilidad Electromagnética

Por sus siglas en inglés EMC (de Electromagnetic Compatibility) <sup>5</sup>, se refiere a la habilidad en que un sistema electrónico puede [3]

- Funcionar apropiadamente en el ambiente electromagnético de trabajo (susceptibilidad).

- No ser una fuente de ruido en ese ambiente electromagnético (emisión).

<sup>&</sup>lt;sup>4</sup>Las ratlines sirven como guía para el diseñador y son eliminadas cuando se realiza alguna conexión eléctrica entre los pads que son unidos por este.

<sup>&</sup>lt;sup>5</sup>Ambos términos se utilizarán indistantemente en el desarrollo de este trabajo.

#### Susceptibilidad

Capacidad de un dispositivo de interactuar con energía electromagnética no deseada. El antónimo es «inmunidad».

#### **Emisión**

Se refiere al potencial que presenta el dispositivo de causar interferencias. Las medidas de EMC están orientadas a limitar la energía electromagnética emitida (o irradiada) y por lo tanto a controlar el ambiente electromagnético en que se desempeña este dispositivo.

El equipo que emite interferencias no necesariamente es susceptible a las mismas, pero también es posible que el dispositivo sea sensible a sus propias emisiones.

Dada la gran diversidad de dispositivos electrónicos que pueden hacer de fuentes en distintos rangos de frecuencia y dado que sería muy complicado y costoso incluir en el diseño de ciertos dispositivos (de bajo costo) consideraciones que los vuelvan inmunes al EMI, existen normas que limitan los niveles de emisión que pueden alcanzar todos los dispositivos electrónicos.

#### 2.2.2. Regulaciones de EMC

En este trabajo se tomó como referencia la norma de la Comisión Federal de Comunicaciones (por sus siglas en inglés, FCC) <sup>6</sup>. En particular se vió la parte 15, subparte B, «Estándares técnicos para equipamiento de cómputo».

Esta norma alcanza cualquier producto que utilice circuitos digitales que funcionan con frecuencias superiores a  $9\ KHz$  [4]. y contempla dos clases:

- Clase A: Dispositivo industrial.

- Clase B: Dispositivo residencial.

De 0.15 a 30~MHz se contemplan las emisiones a la red de alimentación alterna doméstica y de 30~[MHz] a 1~GHz se controla las emisiones que genera el dispositivo bajo prueba. El último punto es de interés para el desarrollo del PCB (no se usa la red de alimentación alterna).

La tabla 2.1 muestra los límites de las emisiones para un dispositivo de clase B.

<sup>&</sup>lt;sup>6</sup>Existen otras normativas como las de la Unión Europea, CISPR (del francés: Comité International Spécial des Perturbations Radioélectriques), cuyo contenido, para el alcance de este trabajo, es el mismo.

| Límites FCC Clase B de emisiones irradiadas medidas a $3\ m$ . |                                    |                                   |  |  |  |  |  |  |  |

|----------------------------------------------------------------|------------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| Frecuencia (MHz)                                               | Intensidad del campo ( $\mu V/m$ ) | IntensidaD de campo ( $dB\mu V/m$ |  |  |  |  |  |  |  |

| 30-88                                                          | 100                                | 40.0                              |  |  |  |  |  |  |  |

| 89-216                                                         | 150                                | 43.5                              |  |  |  |  |  |  |  |

| 216-960                                                        | 200                                | 46                                |  |  |  |  |  |  |  |

| > 960                                                          | 500                                | 54.0                              |  |  |  |  |  |  |  |

Tabla 2.1: Límites de raduación FCC a 3 m.

Nota. Fuente: CFR (Council on Foreign Relations) - Título 47 - Capítulo I - Subcapítulo A - Parte 15 - Subparte B - Sección 15.109, *Radiated emission limits*.

#### 2.3. Radiaciones de Circuitos Digitales

Un circuito digital genera campo electromagnético en modo diferencial o en modo común.

#### 2.3.1. Modo Diferencial

Las radiaciones en modo diferencial son causadas por una señal de corriente que recorre un loop <sup>7</sup> formado por pistas o conectores de cualquier circuito.

Este modo se puede modelar pensando a la estructura que genera la interferencia como una antena loop de dimensiones pequeñas (menor a  $\lambda/4$ ). A continuación se mostrará una expresión que estima el campo eléctrico a 3~m de una antena loop.

La magnitud del campo eléctrico lejano  $|\vec{E}|$  en un loop de corriente pequeño ( $d << \lambda$ , donde d es el diámetro del loop y  $\lambda$  es la longitud de onda de la señal que pasa por este) se puede resumir a la ecuación 2.1 [5].

$$|\vec{E}| = \frac{120\pi^2 I \sin(\theta)}{r} \frac{Af^2}{C^2}$$

(2.1)

#### Donde:

- r es la distancia a la que se mide el campo en m.

- *I* es la corriente que pasa por el loop en *A*.

- f es la frecuencia en I en Hz.

- $\theta$  es el ángulo de azimuth con el que se observa el loop.

<sup>&</sup>lt;sup>7</sup>Se emplea el término en inglés «loop» en lugar del término en castellano «lazo», para guardar la relación con el término «antena loop», término usado en la bibliografía consultada.

- A es el área del loop en  $m^2$ .

- C es la velocidad de la luz,  $3 \times 10^8 \ m/s$ .

Simplificando las constantes se tiene:

$$|\vec{E}| = (13.16 \times 10^{-15}) \frac{I \sin(\theta) A f^2}{r}$$

(2.2)

La ecuación 2.2 muestra que la dependencia de la frecuencia es cuadrática y su validez es en el espacio libre, sin embargo, las mediciones de EMC son realizadas en un área abierta bajo un plano de masa, esta superficie reflectora creada por el plano de masa otorga una ganancia de  $+6\ dB$  a la magnitud de campo eléctrico [3], entonces se reformula la expresión para el campo agregando un factor multiplicador de valor 2 (el equivalente en veces de  $+6\ dB$ ). Si también se reemplaza  $r=3\ m$  se tiene una expresión aproximada para la magnitud de campo  $|\vec{E}_{TEST}|$  que se mediría en un loop de corriente en las pruebas de EMC.

$$|\vec{E}_{TEST}| = (8.77 \times 10^{-15}) I \sin(\theta) A f^{2}$$

(2.3)

La ecuación 2.3, de forma resumida, indica que el campo eléctrico a  $3\ [m]$  de distancia de un loop por donde pasa corriente a una frecuencia tal que  $d << \lambda$ , depende de la intensidad de la corriente, el ángulo respecto de la perpendicular al plano del loop, el área y el cuadrado de la frecuencia.

La dependencia cuadrática de la frecuencia exige que se deba evitar armónicos en lo posible para disminuir la magnitud del campo eléctrico irradiado. Otra opción es reducir la magnitud de la corriente que pasa por los cables. La última posibilidad es en general minimizar el área de los loops de corriente, teniendo especial cuidado con las señales de alta frecuencia.

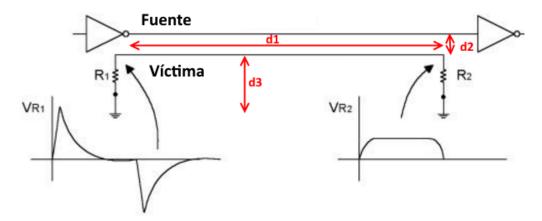

#### 2.3.2. Modo Común

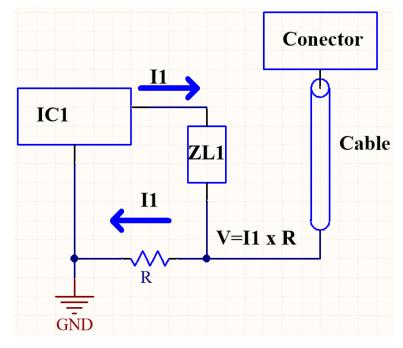

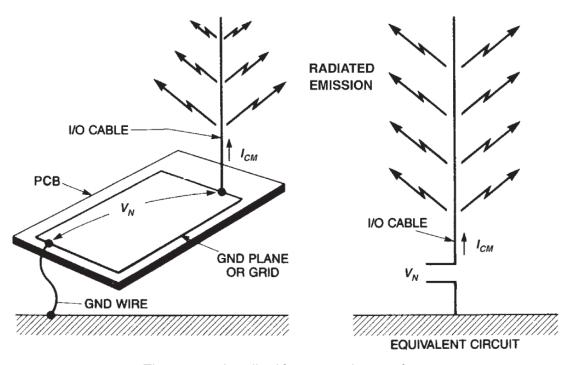

Las radiaciones en modo común son causadas por la diferencia de voltaje causadas en el plano de masa por la corriente de retorno de los circuitos. Cuando algún cable es conectado al plano de masa estas diferencias de tensión causadas los alimentan y hacen que funcionen como antenas, esto se presenta en las figuras 2.4 y 2.3:

# 2.4. Comportamiento de componentes pasivos en radiofrecuencia

Los componentes pasivos como resistencias bobinas y capacitores cambian su respuesta conforme aumente la frecuencia del voltaje o tensión, a continuación se tratarán

Figura 2.3: Tensión V usando el cable como antena.

Figura 2.4: Irradiación en modo común.

Nota. Fuente: Ott, Henry Electromagnetic Compatibility Engineering (pg. 465).

las distintas respuestas de cada uno de estos componentes.

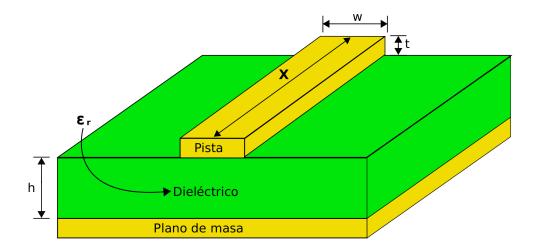

#### 2.4.1. Pistas de cobre

Las conexiones en un PCB entre distintas terminales (o pads) son realizadas con pistas de cobre («tracks» o «traces»), idealmente esta conexión es de conductividad infinita e inductancia nula. En la práctica esta situación no se cumple.

El alejamiento de comportamiento de las pistas de su respuesta ideal se atenúa con el aumento de frecuencia. La conductividad finita no es tanto un problema pero la inductancia de una pista puede llegar a causar problemas de degradación de señal.

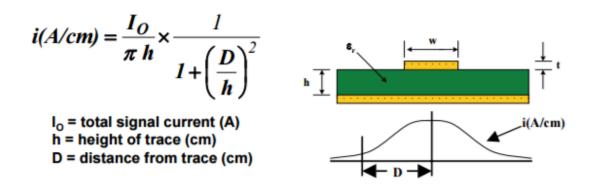

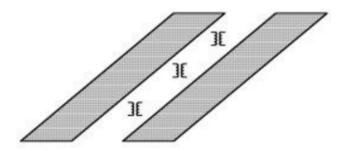

La inductancia (L) de una pista es determinada por el grosor del cobre, el largo y ancho de la pista, y la distancia de la pista al plano de masa [6] según la ecuación 2.4.

$$L = 2X \ln \left( \frac{5.98h}{0.8w + t} \right) nH \tag{2.4}$$

Donde:

- X es el largo de la pista en cm.

- h es la separación entre el plano de masa y la pista en cm.

- w es el ancho de la pista en cm.

- t es el grosor del cobre en cm.

Las dimensiones mencionadas se pueden visualizar en la figura 2.5.

Figura 2.5: Dimensiones de pista que definen inductancia.

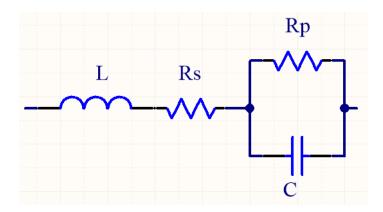

#### 2.4.2. Capacitores

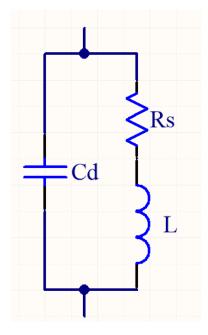

El comportamiento del capacitor real puede ser modelado empleando el circuito de componentes ideal mostrado en la figura 2.6[7].

Figura 2.6: Modelo que aproxima un capacitor real.

La impedancia ( $Z_C$ ) a los extremos del circuito mostrado en la figura 2.6 se puede expresar con la ecuación 2.5.

$$Z_C = R_s + \frac{R_p}{1 + (\omega R_p C)^2} + j \left(\omega L - \frac{\omega R_p^2 C}{1 + (\omega R_p C)^2}\right) \Omega$$

(2.5)

#### Donde:

- $R_s$  es la resistencia que representa las pérdidas en disipación de calor (se puede expresar en función del factor de disipación, del cual se hablará más adelante) en  $\Omega$ .

- $R_p$  es la resistencia que modela las corrientes de fuga en el dieléctrico en  $\Omega$ .

- *L* inductancia de los terminales y las placas que forman el capacitor en *H*.

- $\blacksquare$  C capacidad en F.

- $\omega$  es la frecuencia angular ( $\omega = 2\pi f$ ).

Si se toman los siguientes valores correspondientes a un capacitor cerámico de encapsulado 0603:  $C=0.1~\mu F$ ,  $R_s=0.05~\Omega$ ,  $R_p=100~G\Omega$ , L=850~pH y se grafica la magnitud de la impedancia que presenta este modelo en función de la frecuencia usando la ecuación 2.5, se obtiene el resultado mostrado en la figura 2.7.

Figura 2.7: Respuesta frecuencia-impedancia de un capacitor cerámico.

Como se ve en la figura 2.7, existen dos zonas marcadas para el comportamiento frecuencia-impedancia del capacitor. La primera zona, de pendiente negativa corresponde a la zona capacitiva (la impedancia disminuye conforme aumenta f) que es una zona que coincide hasta un determinado rango de frecuencia con la curva de impedancia para un capacitor ideal (curva discontinua) determinada por la ecuación 2.6.

$$|Z_{L\ IDEAL}| = \frac{1}{\omega C} \tag{2.6}$$

La parte del gráfico con pendiente positiva corresponde a la zona inductiva (linea continua) del capacitor.

Entre  $10^6$  y  $10^8$  Hz, se da la transición entre las dos zonas (punto de inflexión), la frecuencia en este punto es denominada «frecuencia de resonancia»  $(f_r)$ .

Es de mucha importancia conocer la característica en frecuencia de los capacitores que se emplean en el diseño del PCB, especialmente cuando estos se utilicen para desacoplar circuitos que trabajan en altas frecuencias.

#### 2.4.3. Factor de disipación

Por sus siglas en inglés, DF, es el cociente entre la Resistencia Equivalente en Serie (ESR, por sus siglas en inglés) y la reactancia del capacitor  $(X_c)$ . Es expresado como muestra la ecuación 2.7.

$$DF = \frac{ESR}{X_C} \times 100\% \tag{2.7}$$

La ESR es la resistencia (sin tomar en cuenta las partes reactivas) que se ve a los extremos del capacitor, se aproxima con la ecuación 2.8.

$$ESR \approx R_s$$

(2.8)

DF es la inversa del factor de calidad, Q.

$$DF = \frac{1}{Q} \tag{2.9}$$

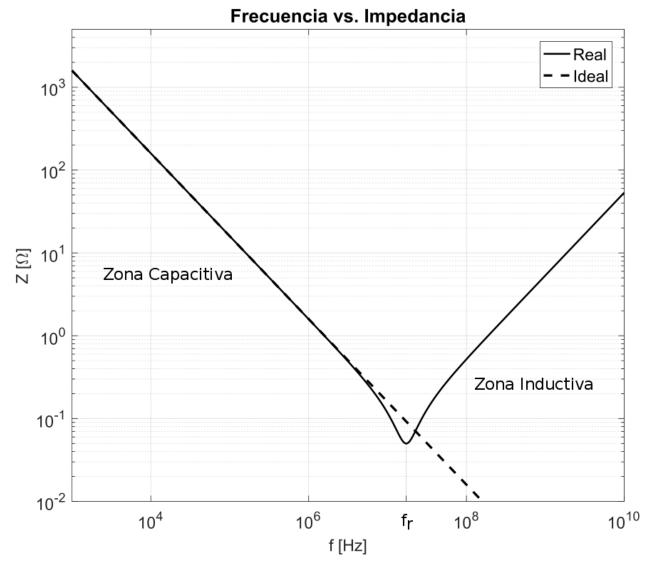

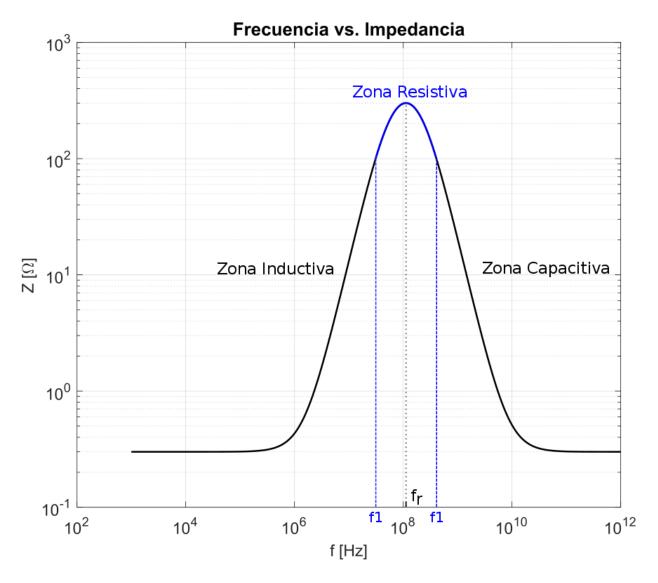

#### 2.4.4. Capacitores en paralelo

El comportamiento en frecuencia del capacitor depende de la ESR y de la inductancia equivalente en serie (ESI, por sus siglas en inglés). La ESI no es otra cosa que el valor de inductancia L en el modelo mostrado en la figura 2.6.

Para saber si el capacitor es adecuado o no para desacoplar un circuito que funciona a una determinada frecuencia, se debe observar si la impedancia del capacitor es relativamente baja alrededor de esta frecuencia. Una forma rápida de determinar esto, es ver si la frecuencia de trabajo del circuito a desacoplar esta en un rango comprendido entre  $0.01f_r$  y  $100f_r$ .

Distintos capacitores tienen distintos valores de ESR y ESI, que determinan una  $f_r$ . A su vez,  $f_r$  determina en que rango de frecuencia la impedancia está por debajo de un determinado nivel. Por ejemplo, la figura 2.7 muestra que el capacitor presenta una impedancia por debajo de  $10~\Omega$  entre 100~KHz y 1~GHz, pero se encuentra por encima de  $1~K\Omega$  por debajo de 1~KHz.

Para presentar una situación concreta, en la figura 2.8 se muestran tres respuestas en frecuencia:

■ Respuesta en frecuencia de un capacitor cerámico de encapsulado 0603 con  $C=1~\mu F,~ESR=0.05~\Omega$  y ESI=850~pH ( $C_{CER}$ , curva continua).

- Respuesta en frecuencia de un capacitor de tantalio encapsulado «A», de  $1~\mu F$ ,  $ESR=1.5~\Omega$  y ESI=2600~pH ( $C_{TANT}$ , curva discontinua).

- Respuesta en frecuencia de ambos capacitores en paralelo ( $C_{PAR}$ , curva punteada).

Figura 2.8: Curvas frecuencia vs. impedancia correspondientes a  $C_{CER}$ ,  $C_{TANT}$  y  $C_{PAR}$ .

Como se puede apreciar en la figura 2.7, la impedancia que presenta el capacitor equivalente es determinada por el capacitor de tantalio en baja frecuencia y por el capacitor cerámico en alta frecuencia. El rango de frecuencias en que la impedancia del capacitor  $C_{PAR}$  está por debajo de  $10~\Omega$ , es aproximadamente de 10~Khz a 1~GHz, rango que mejora la respuesta individual de  $C_{CER}$  y  $C_{TANT}$ .

Julca Yaya, Juan José Diciembre de 2016 Página 16

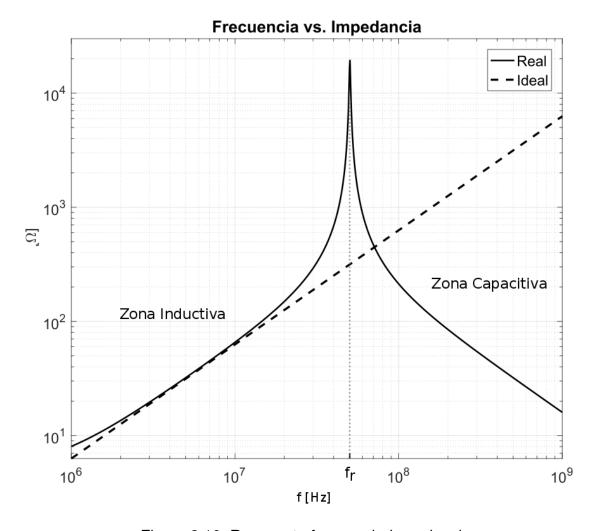

#### 2.4.5. Inductores

Un inductor real se puede modelar con el circuito de la figura 2.9. La impedancia  $(Z_L)$

Figura 2.9: Modelo de un inductor real.

que presenta el circuito de la figura 2.9 corresponde a la ecuación 2.10.

$$Z_L = \frac{R_s + j\omega L}{(1 - \omega^2 L C_d) + j\omega R_s C_d} \Omega$$

(2.10)

Donde:

- $R_s$  es la resistencia del conductor no ideal con el cual se fabrica el inductor en  $\Omega$ .

- $C_d$  es la capacidad equivalente constituida por el paralelo de todas las capacidades parásitas que se forma entre cada par de espiras contiguas del inductor en F.

- $\blacksquare$  L es la inductancia en H.

La figura 2.10 muestra como varía la magnitud de la impedancia (— $Z_L$ —) en función de la frecuencia.

Figura 2.10: Respuesta frecuencia-impedancia

Como se puede apreciar en la figura 2.10, al igual que el capacitor, el inductor tiene una zona inductiva y una zona capacitiva. A frecuencias bajas, la impedancia aumenta (zona inductiva), y luego de la frecuencia de resonancia el comportamiento es el de un capacitor (zona capacitiva).

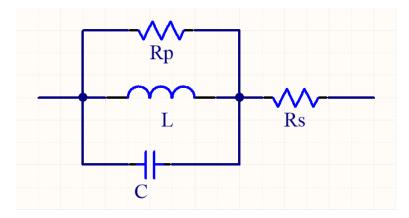

#### 2.4.6. Chips de ferrite

Los chips de ferrite (del inglés, «Ferrite Bead») son dispositivos pasivos cuyo comportamiento en frecuencia se aprovecha para filtrar señales de alta frecuencia. Para entender su comportamiento se parte de analizar el comportamiento del circuito equivalente que se muestra en la figura 2.10 [8]. De la figura 2.10 se puede llegar a la ecuación ??, que es la expresión para la impedancia del chip de ferrite.

$$Z_{FB} = Rs + \frac{\omega^2 R_p L^2}{R_p^2 (1 - \omega^2 C L)^2 + (\omega L)^2} + j \frac{\omega R_p^2 L (1 - \omega^2 C L)}{R_p^2 (1 - \omega^2 C L)^2 + (\omega L)^2} \Omega$$

(2.11)

Figura 2.11: Modelo de un chip de ferrite.

#### Donde:

- $R_p$  es la resistencia de AC, se da cuando el ferrite es puramente resistivo (en  $f = f_r$ ), se expresa en  $\Omega$ .

- $R_S$  es la resistencia de los conductores imperfectos en  $\Omega$ .

- C es la capacidad que domina el comportamiento del ferrite en altas frecuencias, se expresa en F.

- L es la inductancia que domina el comportamiento del ferite en bajas frecuencias, se expresa en H.

Por ejemplo, si se evalúa la magnitud de esta impedancia ( $|Z_{FB}|$ ) con  $R_S=300~m\Omega$ ,  $R_p=300~\Omega$ , C=2~pF y  $L=1~\mu H$  para distintas frecuencias se obtiene la respuesta mostrada en la figura 2.12.

La figura 2.12 evidencia la existencia de 3 zonas en el comportamiento en frecuencia del chip de ferrite: Zona inductiva, capacitiva y resistiva. En un principio la curva guarda cierta similaridad con la curva del inductor mostrada en la figura 2.10 por las zonas inductivas y capacitivas. La diferencia yace en la zona resistiva, la cual es una zona alrededor de la frecuencia de resonancia en que la magnitud de la impedancia tiene una variación pequeña en relación a la variación abrupta que se observa en al curva de la figura 2.10.

Los chips de ferrite pueden ser usados para filtrar altas frecuencias y para emplearlos de forma correcta se deberá verificar la curva de funcionamiento y asegurarse que los ruidos de alta frecuencia que se desean filtrar sean del orden de  $f_r$  (el ferrite del ejemplo sería ideal para filtrar ruidos de  $100\ MHz$ ).

Figura 2.12: Curva frecuencia vs. impedancia correspondiente a un chip de ferrite.

### Capítulo 3

# Diseño del esquemático del PCB en software CAD

En este capítulo se describen los procedimientos de diseño del esquemático del PCB, el cual se encuentra basado en el prototipo de sistema de control embebido realizado en la plataforma CIAA [1].

#### 3.1. PCB basado en plataforma CIAA

La CIAA (Computadora Industrial Argentina) es la plataforma sobre la cual se realizó el prototipo del sistema de control embebido que se desea implementar en un PCB de propósito específico. Para la implementación del prototipo se utilizó la versión educativa de la CIAA, llamada «CIAA EDU NXP» que usa un microcontrolador *NXP LPC4337*. El diseño entonces, se debe basar en este prototipo realizado, lo cual impone las siguientes consignas:

- El PCB debe integrar todos los sensores con los que cuenta el prototipo.

- Los sensores deberán de conectarse al microcontrolador de la misma forma que el prototipo de tal forma que se pueda reutilizar el mismo firmware.

- Se deberán incorporar únicamente los sensores y dispositivos necesarios para el funcionamiento del sistema de control embebido.

#### 3.2. Biblioteca de componentes

Todos los componentes tienen un diagrama eléctrico o esquemático, este hace referencia a sus terminales físicos por pines. Por ejemplo, el microcontrolador LPC4337 tiene

#### CAPÍTULO 3. DISEÑO DEL ESQUEMÁTICO DEL PCB EN SOFTWARE CAD

Página 22

un esquemático de 144 pines. Los componentes a su vez pueden ser divididos en subcomponentes, o partes. Por ejemplo el LPC4337 tiene sus 144 pines repartidos en 19 partes, los pines estan agrupados según su funcionalidad.

El circuito general realiza las conexiones entre los pines de cada componente, a su vez los esquemáticos propios de cada componente son organizados en una biblioteca de componentes.

Altium ofrece una herramienta para gestionar las bibliotecas, se verificó la correcto asignación de pines de cada uno de los componentes según su hoja de datos. La importancia de este procedimiento radica en que luego se generará un mapa de conexiones en el desarrollo del PCB, que asocia cada designador de pin con una conexión física en un plano del componente (mapa o «footprint»). Un pin mal asignado en esta instancia puede significar un cambio de polaridad en la alimentación, por ejemplo.

#### 3.3. División del esquemático

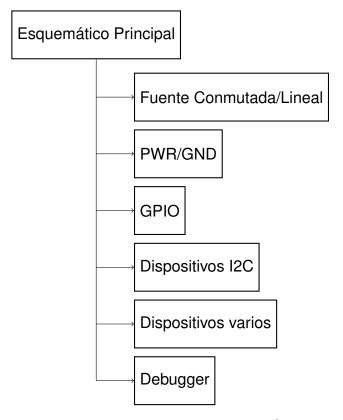

El diseño del esquemático se realizó en *Altium Designer*, programa que permite crear varios subesquemáticos unidos en un esquemático principal (estructura jerárquica). La estructura jerárquica permite organizar el diseño en bloques, la estructura que se definió como se muestra en la figura 3.1.

#### 3.4. Esquemático Principal

El esquemático principal (se muestra en la figura A.1 del anexo) contiene las conexiones que se detallan a continuación.

#### 3.4.1. Circuito Oscilador

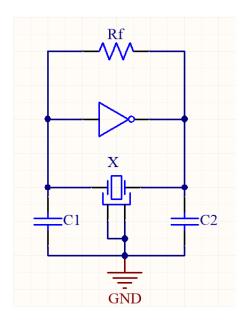

El microcontrolador LPC4337 funciona con un clock generado por un oscilador Pierce a cristal, el circuito básico de este tipo de oscilador se muestra en la figura 3.2. En esta figura se muestran sus componentes: un amplificador inversor, una resistencia de realimentación  $(R_f)$ , un cristal (X) y dos capacitores (C1 y C2).

El amplificador inversor realimenta a través del cristal, el cual sirve como filtro a una frecuencia determinada (en este caso  $12\ MHz$ ). Los capacitores  $C1\ y\ C2$  proveen un corrimiento de fase, que en conjunto con los  $180^\circ$  que establece el amplificador inversor constituyen un corrimiento de fase nulo, en otras palabras la señal en la entrada y en la salida estan en fase. Si se agrega que la ganancia del amplificador inversor cumple G>1 se cumple el criterio de Barkhausen. La resistencia Rf es una resistencia de polarización

Figura 3.1: Estructura del esquemático.

que mantiene al inversor en su región lineal de trabajo. La hoja de datos del LPC4337 recomienda que se usen valores entre 18 y 27 pF, se determinaron: C1 = C2 = 20 pF.

Tanto el cristal como los capacitores se conectan a los pines 12 y 13 del microcontrolador tal como se muestra en la figura A.1 del anexo. No se requiere proveer ni Rf ni el amplificador inversor, los cuales son incluidos en el microcontrolador.

Figura 3.2: Circuito del oscilador Pierce

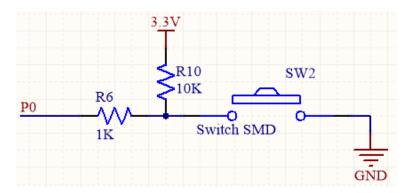

#### 3.4.2. Botón de Reset

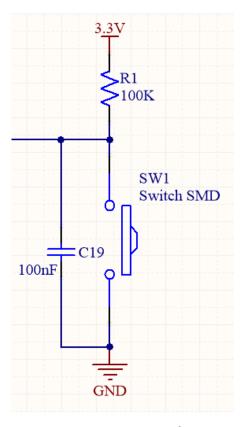

Se incluye un botón para aplicar un reset por hardware al microcontrolador. El botón es del tipo normal abierto, tal como se muestra en la figura 3.3. También se incluye una salida de reset por el conector P1, la cual tiene un diodo de protección (cátodo a la salida del conector y ánodo hacia el pin reset).

Un lado del botón se encuentra a GND, mientras que el otro al pin 128 del microntrolador (pin reset activo por bajo). Este punto se mantiene en nivel alto a través de una resistencia de pull up. El capacitor en paralelo a la entrada de reset hace que se mantenga el nivel bajo que se presenta al presionar el botón por al menos  $10\ ms$  pese a que el botón regrese a su estado normal abierto. Para comprobar esta afirmación, se realizó una simulación en *LTspice*, la cual se presenta en la figura 3.4.

Figura 3.3: Circuito del botón de reset.

Figura 3.4: Circuito de simulación del botón reset.

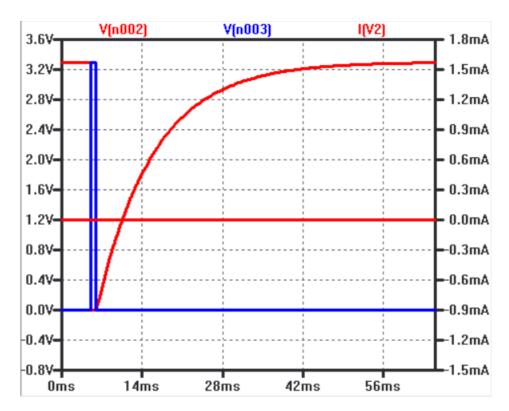

Se utilizó para modelar el botón una llave programada para cerrarse por  $1\ ms$  con un tiempo de transición de  $1\ ns$ , el resultado de la simulación en estado transitorio se muestra en la figura 3.5, la cual muestra en trazo azul el tiempo en que está abierto el switch si no hubiera un capacitor en paralelo y la respuesta con el capacitor. Se observa que cuando está presente el capacitor, presionar el botón de reset por  $1\ ms$  implica dejar el botón reset en estado bajo (menor a  $2.2\ V$ ) por al menos  $10\ ms$ . Al mismo tiempo de establecer un nivel prolongado de permanencia en nivel bajo, se filtra el efecto rebote (del inglés, «bouncing») que presenta cuando se acciona cualquier tipo de interruptor mecánico.

# 3.4.3. Conversores analógico-digitales

Se utilizan 6 de los 7 canales del ADC, 3 son usados para las señales de entrada del sensor de voltaje, corriente y presión diferencial, mientras que otros 3 son llevados a un conector. Todos los conversores tienen una resistencia en serie de  $1.2~K\Omega$ , el motivo de esta resistencia en serie es reducir en una pequeña proporción la máxima tensión de entrada al hacerse un divisor resistivo con los  $1.2~M\Omega$  que tienen todos los conversores como impedancia de entrada. También funcionan como limitador de corriente por si el pin se configura por software a un nivel bajo aún cuando está presente la señal del sensor. Los pines ADC del microcontrolador son:

- Pines 2, 143 y 149 para sensores del controlador.

- Pines 138,142,144 como entradas ADC en el conector de salida del conector P1.

Figura 3.5: Resultado de la simulación del botón reset

#### 3.4.4. Conversor digital-analógico

El pin 6 del microcontrador puede ser configurado como un DAC, este pin estará disponible en el conector P1 del esquemático principal. Una resistencia de  $470~\Omega$  funciona como limitador de corriente.

#### 3.4.5. Salidas de alimentación

Por el conector P1 también se provee salidas de tensión de 5 y 3 V, también conexiones a GND y GND analógica. La conexión a las tensiones se realizan por medio de un fusible resetable PTC (del inglés Positive temperature coefficient) de montaje superficial (TH1) que limita la corriente a  $300 \ mA$ .

## 3.5. Fuente Conmutada

El sistema de control embebido deberá funcionar alimentándose de baterías que no proveen los niveles de tensión que requieren los integrados que lo componen, los cuales son  $5\ V$  y  $3.3\ V$ , por ello se deberá recurrir a distintos reguladores de voltaje.

Un factor determinante es que el sistema debe mantener el menor nivel de consumo posible, por lo tanto para obtener la tensión de  $5\ V$  se deberá priorizar la eficiencia. El tipo de regulador que destaca en este aspecto es uno conmutado, entonces se diseñó

una fuente de poder conmutada o SMPS (por sus siglas en inglés Switching Mode Power Supply). El circuito a implementar es específicamente un «Buck Converter», que es un tipo de regulador conmutado que fija la salida a una tensión menor que la entrada. Se partió del diagrama básico del circuito propuesto en la hoja de datos del LM2596 de ON-Semiconductor, a partir de este se añadieron circuitos de protección (descritos más adelante en esta sección) para hacer más robusta la fuente. El esquemático del regulador a  $5\ V$  se presenta en la figura 3.6.

Figura 3.6: Circuito de la fuente conmutada

#### 3.5.1. Filtro LC

Para simplificar el proceso de selección de estos componentes, se tomó el valor de la tabla de la hoja de datos del regulador para una elección rápida del inductor  $L_1$  y capacitor  $C_{21}$ .

| CONDITIONS               |                        |                             | INDUCTOR        |              | OUTPUT CAPACITOR                  |                                 |                             |                                  |

|--------------------------|------------------------|-----------------------------|-----------------|--------------|-----------------------------------|---------------------------------|-----------------------------|----------------------------------|

|                          |                        |                             |                 |              | THROUGH-HOLE ELECTROLYTIC         |                                 | SURFACE-MOUNT TANTALUM      |                                  |

| OUTPUT<br>VOLTAGE<br>(V) | LOAD<br>CURRENT<br>(A) | MAX INPUT<br>VOLTAGE<br>(V) | INDUCTANCE (µH) | INDUCTOR (#) | PANASONIC<br>HFQ SERIES<br>(µF/V) | NICHICON<br>PL SERIES<br>(μF/V) | AVX TPS<br>SERIES<br>(µF/V) | SPRAGUE<br>595D SERIES<br>(µF/V) |

| 3.3                      | 3                      | 5                           | 22              | L41          | 470/25                            | 560/16                          | 330/6.3                     | 390/6.3                          |

|                          |                        | 7                           | 22              | L41          | 560/35                            | 560/35                          | 330/6.3                     | 390/6.3                          |

|                          |                        | 10                          | 22              | L41          | 680/35                            | 680/35                          | 330/6.3                     | 390/6.3                          |

|                          |                        | 40                          | 33              | L40          | 560/35                            | 470/35                          | 330/6.3                     | 390/6.3                          |

|                          |                        | 6                           | 22              | L33          | 470/25                            | 470/35                          | 330/6.3                     | 390/6.3                          |

|                          | 2                      | 10                          | 33              | L32          | 330/35                            | 330/35                          | 330/6.3                     | 390/6.3                          |

|                          |                        | 40                          | 47              | L39          | 330/35                            | 270/50                          | 220/10                      | 330/10                           |

| 5                        | 3                      | 8                           | 22              | L41          | 470/25                            | 560/16                          | 220/10                      | 330/10                           |

|                          |                        | 10                          | 22              | L41          | 560/25                            | 560/25                          | 220/10                      | 330/10                           |

|                          |                        | 15                          | 33              | L40          | 330/35                            | 330/35                          | 220/10                      | 330/10                           |

|                          |                        | 40                          | 47              | L39          | 330/35                            | 270/35                          | 220/10                      | 330/10                           |

|                          |                        | 9                           | 22              | L33          | 470/25                            | 560/16                          | 220/10                      | 330/10                           |

|                          | 2                      | 20                          | 68              | L38          | 180/35                            | 180/35                          | 100/10                      | 270/10                           |

|                          |                        | 40                          | 68              | L38          | 180/35                            | 180/35                          | 100/10                      | 270/10                           |

Tabla 3.1: Tabla de selección rápida de capacitor/inductor de filtro **Nota**. Fuente: Nota de aplicacón SNVS124D de Texas Instrument (pg. 23) .

La fila resaltada de la tabla 3.1, la cual corresponde a voltaje de salida 5~V y corriente máxima de 3~A, detalla los siguientes valores :  $L_1=47~\mu H$  y que  $C_{21}=330~\mu F$ . El inductor para el valor mostrado y para la corriente, adicionalmente se determinó que los tipos encapsulados o «shielded» pueden suprimir el campo irradiado, mejorando la EMC del PCB final. Para el capacitor de salida también se elige uno que presente tanto la capacidad y voltaje determinados como que se clasifique de baja resistencia equivalente en serie o «Low ESR» (por sus siglas en inglés, Equivalent Series Resistance).

## 3.5.2. Diodo de freewheeling

La elección del diodo de freewheeling  $(D_3)$  se orientó por el camino del bajo consumo de potencia. Por este diodo circulará la misma corriente salida durante el tiempo que el switch bloquea la tensión de entrada. Esta corriente junto con la caída directa del diodo  $V_D$  determinan la potencia del diodo  $P_D$  según la ecuación 3.1.

$$P_D = I_{max} \times V_D \tag{3.1}$$

Un diodo Schottky presenta menor tensión directa frente a un diodo de recuperación rápida (fast recovery diode). El primero presenta caídas típicas entre 0.3 a 0.6 V mientras que el segundo 0.8 a 1.1 V. Como se desea mantener la eficiencia lo más alto posible se consideró usar el BC540, el cual es un dispositivo que se acomoda tanto a los voltajes de

Página 29

polarización directa e inversa como al nivel de corriente (acorde con la hoja de datos, este diodo excede en al menos  $50\,\%$  cada una de las especificaciones mencionadas).

#### 3.5.3. Capacitor de entrada

Este capacitor ( $C_{20}$ ) suprime los posibles transitorios de la línea de alimentación y se designa teniendo en cuenta la corriente de ripple RMS,  $I_{C\ RMS}$ , con la fórmula provista en la hoja de datos del LM2596.

$$I_{C~RMS} > 1.2 \times I_{Max} \times \frac{V_{out}}{V_{in}}$$

(3.2)

Si se toma como valor mínimo de alimentación de entrada como 16~V, esto ocasiona un valor de corriente de ripple del capacitor de  $I_{C~RMS}=1.125~A$ . Además de esto, se debe procurar también en este caso un capacitor del tipo LOW ESR. El capacitor que cumple con estos requisitos y que se pudo tener acceso fue uno electrolítico de motanje superficial de  $470~\mu F$ , 50~V,  $0.06~\Omega$  y  $1.19A_{RMS}$ .

#### 3.5.4. Otras consideraciones

La tensión de alimentación ingresa a través de la bornera TB1 (bornera a tornillo de dos terminales con  $5.08\ mm$  de separación entre los mismos) y llega al primer elemento de protección, el diodo rápido  $D_1$  que evita funcionamiento en conexión reversa. El fusible reseteable  $TH_1$  protege contra posibles sobrecorrientes. Es importante definir las características específicas de este de acuerdo a la tensión de entrada y a la corriente de entrada al regulador para una corriente de salida del regulador. Se eligió uno de  $30\ V$  y  $0.35\ A$  pero puede ser cambiado para voltajes/corrientes mayores si fuese necesario.

El jumper  $J_1$  hace que se obvie el regulador de voltaje, siempre y cuando el usuario se asegure de conectar a la entrada de voltaje  $5\ V$ . El diodo  $D_2$  es un supresor de transitorios SZP6SMB11CAT3 de On Semiconductor, protege al regulador de picos de entrada y descargas estáticas y según la hoja de datos tiene un tiempo de respuesta menor a  $1\ ns$ .

El diodo LED en serie con resistencia  $R_2$  de  $1~K\Omega$  sirven para indicar visualmente que la fuente esta funcionando, la corriente que pasa por esta es menor a 3~mA si se considera que la caída de tensión del típica para diodo LED rojo de montaje superficial es 2~V.

El diodo Zener  $Z_1$  en paralelo provee protección adicional que limita el sobrepasamiento de la salida en el transitorio. Para evaluar el comportamiento de esta etapa de protección se simuló en LTSpice el circuito que se presenta en la figura 3.7.

Se simularon dos casos, para carga RL= 5 y 50  $\Omega$ , lo cual para una salida de 5 V implica una corriente de salida de 1 A y 100 mA, respectivamente. Para ambos casos se graficaron las formas de onda de la tensión de salida con y sin el uso del Zener y adicionalmente

Figura 3.7: Circuito de simulación SMPS.

la corriente que pasa por el Zener (cuando está presente, valga la redundancia). Ambas simulaciones se hacen en régimen transitorio, los resultados se presentan en las figuras 3.8 y 3.91: De analizar los dos gráficos, se puede deducir que la protección contra so-

Figura 3.8: (izquierda) tiempo vs. voltaje de salida (derecha) tiempo vs. corriente del Zener para RL= $5 \Omega$ .

brevoltaje del Zener en paralelo también ayuda a disminuir el sobrepasamiento inicial del regulador (el máximo de la curva verde sobre el máximo de la curva azul) y adicionalmente se acorta el tiempo de establecimiento al valor de régimen. El pico de corriente del Zener en este caso dura menos de 1 ms, lo que no representa un nivel peligroso de disipación para el dispositivo que se implementará (potencia máxima de 0.5~W).

<sup>&</sup>lt;sup>1</sup>Ambas figuras tienen dos ejes Y uno para tensión (eje Y izquierdo) y otro para corriente (eje Y derecho)

Figura 3.9: (izquierda) tiempo vs. voltaje de salida (derecha) tiempo vs. corriente del Zener para  $RL=50~\Omega$ .

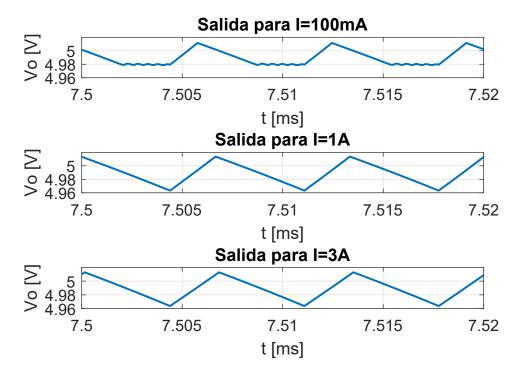

## 3.5.5. Ripple a la salida

Un factor importante de la SMPS es el nivel de ripple a la salida. La aproximación que se tomó fue usar el mismo esquema de simulación de la figura 3.7 para observar el nivel de ripple que verá a la salida para dos tensiones de entrada y para cada tensión evaluar con 3 cargas: 50, 5 y 1.66  $\Omega$ , que derivan en tres corrientes distintas de salida: 100 mA, 1 y 3 A. El resultado de las simulaciones se presenta en las figuras 3.10 y 3.11.

Figura 3.10: Ripple de voltaje para tres corrientes cuando la entrada es  $V_{in} = 16 V$ .

Julca Yaya, Juan José Diciembre de 2016 Página 31

Figura 3.11: Ripple de voltaje para tres corrientes cuando la entrada es  $V_{in} = 24 V$ .

Como se puede apreciar en las figuras 3.10 y 3.11 el nivel de ripple no varia de forma significativa cuando varia la tensión de entrada, pero sí lo hace cuando varía la corriente de salida. Cuando se suministra una corriente de salida de  $I=100\ mA$  se presenta un nivel de ripple  $V_R=40\ mVpp$ , mientras que para una corriente de  $I=1\ A$ , el ripple es de  $V_R=70\ mVpp$ .

## 3.6. Fuente Lineal

Si bien es cierto el nivel de ripple encontrado para la fuente conmutada es relativamente pequeño respecto de la salida nominal  $(70\ mV)$  es el 1.4% de  $5\ V)$  y no afecta de ninguna forma los circuitos digitales, se debe tener en cuenta que no se ha contemplado ningún otro factor que pueda degradar la fuente (ruido térmico y picos de corriente de los mismos circuitos digitales, por ejemplo). Si se generaliza este ripple para una posible etapa conmutada con salida de  $3.3\ V$ , que requiere el microcontrolador y otros dispositivos, se pueden tener errores considerables de mediciones en sensores analógicos.

Para consolidar lo expuesto se puede recurrir al siguiente ejemplo: Si se asume el mismo nivel de ripple que se encontró para el regulador conmutado de  $5\ V$  para la salida de un segundo regulador conmutado de  $3.3\ V$ , el cual alimenta al microcontrolador y a sus conversores analógicos digitales; y se desea adquirir datos del sensor de presión

diferencial MPXV7002, que tiene una sensibilidad da por la ecuación 3.3.

$$S = 1 \frac{KPa}{V} \tag{3.3}$$

Un nivel de ripple en la alimentación de  $70 \ mVpp$  causa un error en la medición (DeltaS) que se puede expresar con la ecuación 3.4.

$$\Delta S = 1 \frac{KPa}{V} \times 70 \ mV = 70 \ Pa \tag{3.4}$$

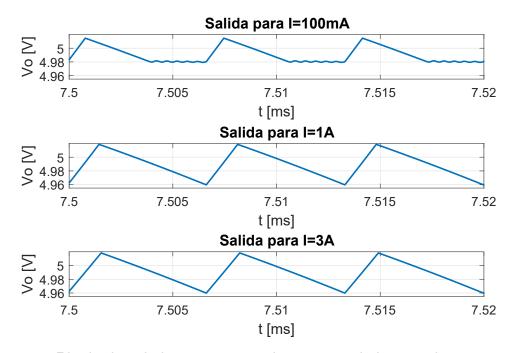

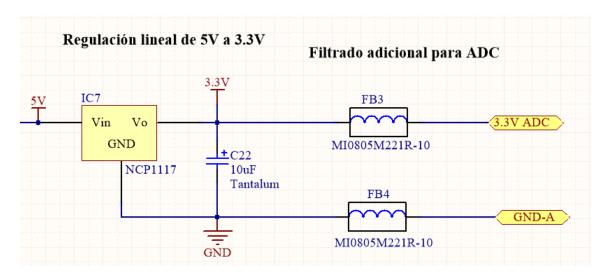

Este error no tiene en cuenta ni el error del sensor ni el ruido que se acopla, se puede experar mayor error en la medición. Para afrontar este problema se plantea una situación de compromiso entre la eficiencia de la fuente y el nivel de ripple que se maneja, el cual se encuentra en usar un regulador lineal LDO (por sus siglas en inglés, Low Drop Out) en serie con el conmutado de  $5\ V$  para generar los  $3.3\ V$ , adicionalmente, se filtrará este voltaje generado usando chips de ferrite o «Ferrite Beads» para alimentar sensores analógicos. El esquemático diseñado en Altium para esta etapa se muestra en la figura 3.12.

Figura 3.12: Regulador lineal con salida 3.3 V y filtrado con ferrites

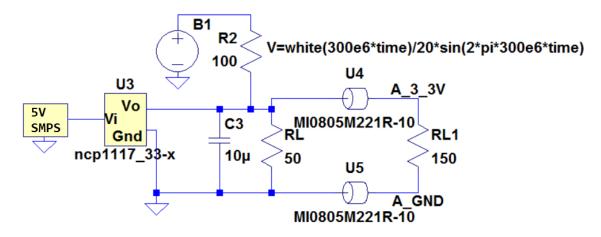

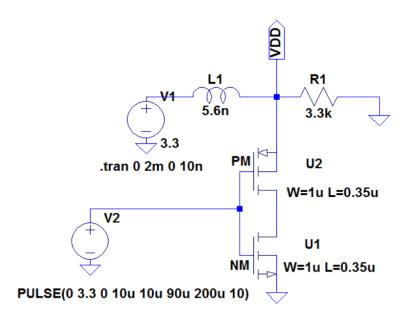

Para verificar el funcionamiento del circuito de la figura 3.12 se realizó nuevamente un esquema de simulación en LTSPICE, el cual consiste en colocar en cascada el regulador lineal mostrado con el regulador conmutado (5 V de SMPS); adicionalmente se inyectó una fuente de ruido a la salida de 3.3~V que a su vez es modulada con una onda sinusoidal de 300~MHz. El motivo de esta modificación es que los ferrites que se usaron como filtro para la tensión y masa analógica son los MI0805M221R-100, los cuales según su hoja de datos presentan una resistencia de  $220~\Omega$  a 100~MHz y de esa forma se está seguro que el ancho de banda de ruido estará por encima de esta frecuencia y se podrá verificar su funcionamiento en la simulación. El esquema de simulación se presenta en la figura 3.13.

Julca Yaya, Juan José Diciembre de 2016 Página 33

Figura 3.13: Esquema de simulación de la fuente lineal con ruido inyectado.

En la figura 3.13 el bloque «5V SMPS» es un diagrama resumido de la fuente SMPS de la figura 3.8 (incluso se han preservado los  $5~\Omega$  de carga para que el regulador lineal se alimente de una línea con ripple de al menos 70~mVpp). El regulador lineal se ha cargado con  $50~\Omega$  y la parte filtrada con  $150~\Omega$ . El comportamiento del regulador determinado al ejecutar la simulación se muestra en la figura 3.14.

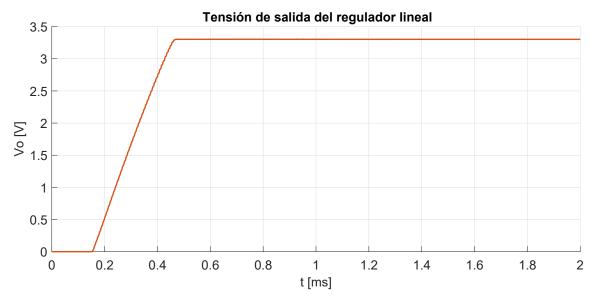

Figura 3.14: Respuesta del regulador lineal.

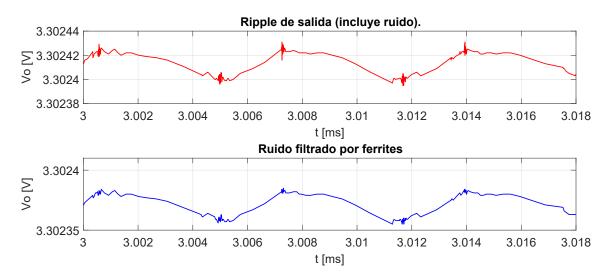

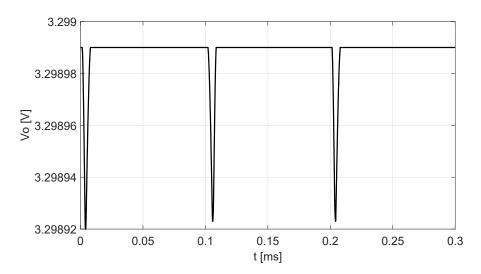

Si se amplia la figura 3.14 en un intervalo dentro de su estado de régimen se puede observar dos situaciones favorables para esta configuración: un bajo nivel de ripple en relación a la fuente conmutada, y la eficacia del filtrado con ferrites. La ampliación es mostrada en la figura 3.15.

El nivel de ripple es menor a  $40~\mu Vpp$ , si se retoma el ejemplo del sensor MPXV7002

Figura 3.15: Ampliación de figura 3.14 en estado de régimen.

se tendrá un error por ripple dado por la ecuación 3.5.

$$\Delta S = 1 \frac{KPa}{V} \times 40 \; \mu V = 40 \; mPa$$

(3.5)

Este resultado es mucho más satisfactorio que el de la contraparte conmutada. El otro lado del compromiso es la pérdida de eficiencia, según la hoja de datos la corriente de reposo máxima del regulador NCP1117 es  $10\ mA$ , que es 100 veces menor a la salida máxima de  $1\ A$  por lo que la fórmula para el cálculo de eficiencia de fuentes lineales LDO se puede resumir a:

$$\eta_{reg3.3V} = \frac{V_{in}}{V_{out}} = \frac{3.3 V}{5 V} \times 100 \% = 73 \%$$

(3.6)

Este resultado es menor al típico 90 % que exhibe el regulador conmutado con LM2596.

## 3.7. PWR/GND

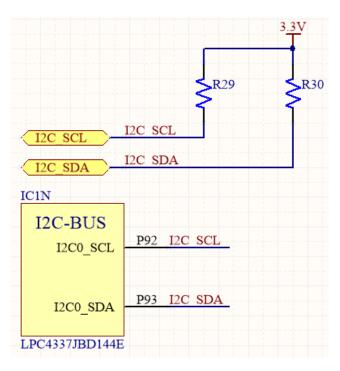

Este esquemático detalla la forma en que se desacoplan los pines de alimentación del microcontrolador, el mismo concepto y criterio de desacoplo se generalizará a todos los circuitos digitales que se implementen.

Desacoplar se refiere a aislar la fuente de los picos de corriente que generan los circuitos digitales. Un elemento característico de la lógica digital es un inversor CMOS (por sus siglas en inglés Complementary Metal-Oxide Semiconductor), un circuito digital cualquiera, como un módulo I2C, puede contener decenas de miles de inversores. Si se considera al inversor como un célula básica contenida en circuitos digitales más complejos, basta evaluar el efecto que tiene un inversor sobre una fuente ideal que lo alimenta sin ningún tipo de desacople.

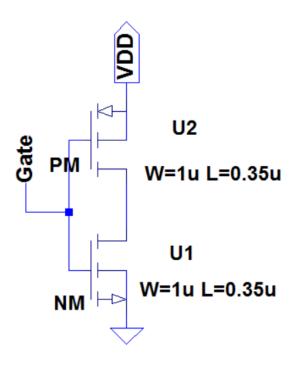

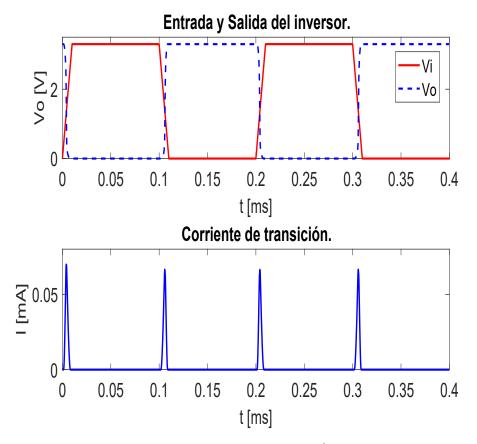

Un inversor CMOS se contruye con dos transistores, un N-MOS y un P-MOS. Para simular se eligieron modelos SPICE para transistores de  $0.35~\mu m$  de ancho de canal, tecnología aún vigente que acepta ser manejada por niveles de 3.3~V. El circuito de simulación del inversor se muestra en la figura 3.16.

Figura 3.16: Inversor con transistores de  $0.35~\mu m$  de ancho de canal.

Se creó un circuito de simulación que trabaja a niveles de 3.3~V (figura 3.17). Se inyecta en los pines GATE de ambos transistores una onda cuadrada a la entrada de 5~KHz y con tiempo de crecimiento de 10~us. Se alimentó al inversor con una fuente ideal con resistencia en serie de  $0.5~\Omega$  y una inductancia que corresponde a una pista de cobre de 1~cm de largo, 2~mm de ancho y grosor correspondiente a un PCB con  $1~oz/in^2~^2$ , 5.6~nH.

La salida, como es de esperarse, se invierte. Lo que se busca resaltar es que existe un periodo de transición entre un cambio de nivel a la salida (producto de un cambio inverso a la entrada, valga la redundancia), por ejemplo en la salida, durante una transición de nivel alto (N-MOS en alta impedancia y P-MOS en baja impedancia) a un nivel bajo (N-MOS en baja impedancia y P-MOS en alta impedancia). Se pasa momentáneamente por un nivel de impedancia media de ambos transistores, la cual ocasiona un pico de corriente, como se muestra en la figura 3.18. El efecto de este pico de corriente sobre la fuente ideal se muestra en la figura 3.19.

La figura 3.19 muestra que un solo inversor puede causar variaciones en la fuente de alimentación de hasta  $0.07\ mV$  respecto de su valor en estado de régimen. Este nivel de

<sup>&</sup>lt;sup>2</sup>Se empleó el calculador de inductacias de la siguiente página: http://chemandy.com/calculators/flat-wire-inductor-calculator.htm.

Figura 3.17: Circuito de simulación con inversor.

Figura 3.18: Resultados de la simulación del inversor.

Figura 3.19: Fuente ideal afectada por conmutaciones del inversor.

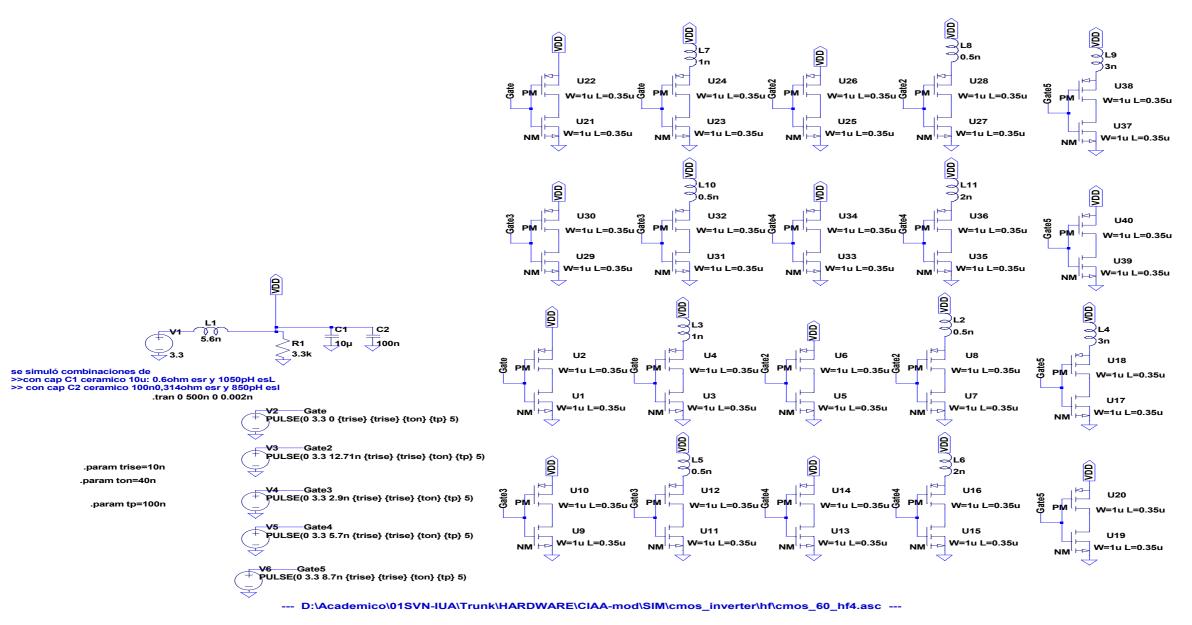

voltaje no es una cifra significativa. Para inspeccionar cual sería el efecto de varios inversores se consideró construir el mismo circuito de simulación con 60 de estos (no se espera un crecimiento lineal) y alimentar estos en grupos arbitrarios por 5 fuentes desfasadas similares a la de la figura 3.17(este circuito de simulación se muestra en la figura B.1 del anexo). El resultado se visualiza en la figura 3.20.

Figura 3.20: Fuente ideal afectada por 60 inversores.

Para el caso de la figura 3.20, la fuente experimenta una variación máxima de  $\pm 1~mV$ , también se resalta el carácter oscilatorio que adquiere cuando los inversores no están en fase. Si se considera que existen miles de circuitos más complejos en todos los dispositivos digitales que se emplearán, se puede esperar variaciones en la fuente de alimentación de varios ordenes por encima del que se ha visto en ambos ejemplos, en este caso el aco-

Julca Yaya, Juan José Diciembre de 2016 Página 38

Página 39

plamiento de estas corrientes a la fuente puede degradarla significativamente, exponiendo el sistema general al fallos por su propio funcionamiento.

Un método de uso masivo para este tipo de situaciones es el uso de un capacitor de desacoplo.

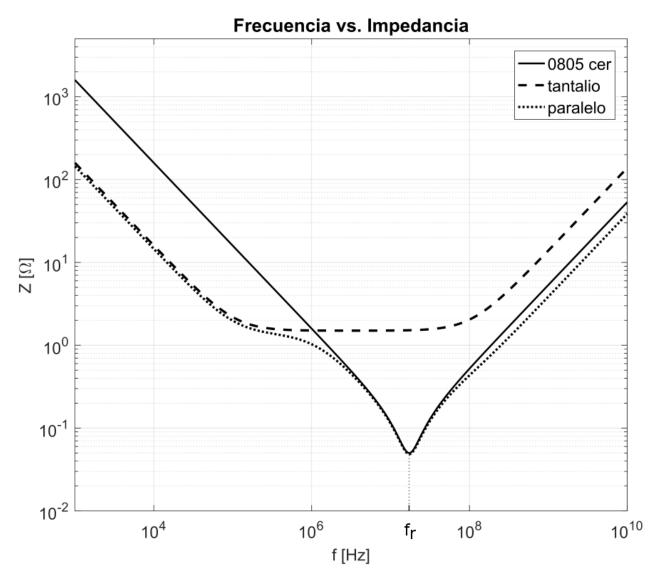

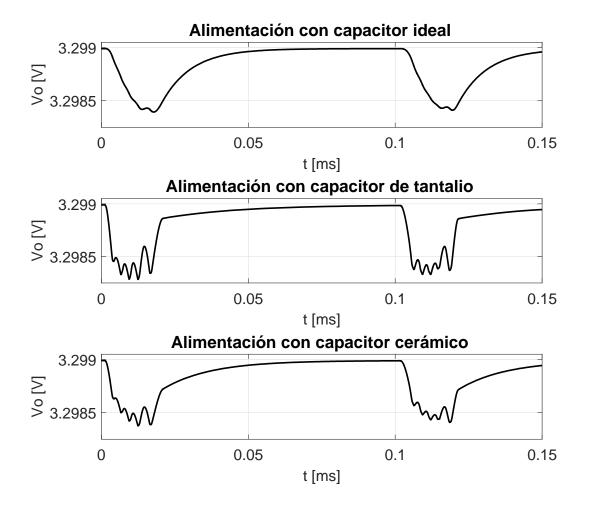

## 3.7.1. Capacitor de desacoplo

Un capacitor de desacoplo (en inglés «Bypass Capacitor») puede aminorar la degradación de la fuente que se muestra en la figura 3.20. Básicamente el capacitor de desacoplo provee la corriente de conmutación de los circuitos digitales antes que esta provenga de la fuente. Para tener una idea del efecto de su empleo, se colocó un capacitor de  $10~\mu F$  en paralelo con la fuente luego de la inductacia de 5.6~nH, que ya se dijo, simula las inductancias de las pistas de conexión.

También se optó por simular el mismo circuito reemplazando el capacitor ideal de  $10~\mu F$  con dos capacitores reales, modelados considerado solo la ESR y la ESI. Ambos parámetros fueron obtenidos de las tablas 3.2 y 3.3. **Nota**. Fuente: Cain, Jeffrey *COMPARISON*

| Tamaño de Encapsulado | Inductancia $(pH)$ |  |  |  |  |

|-----------------------|--------------------|--|--|--|--|

| Cerámico              |                    |  |  |  |  |

| 603                   | 850                |  |  |  |  |

| 805                   | 1050               |  |  |  |  |

| 1206                  | 1250               |  |  |  |  |

| 1210                  | 1020               |  |  |  |  |

| Tantalio              |                    |  |  |  |  |

| R                     | 1600               |  |  |  |  |

| Α                     | 2200               |  |  |  |  |

| В                     | 2250               |  |  |  |  |

| С                     | 2800               |  |  |  |  |

Tabla 3.2: Inductacia equivalente en serie Capacitores Cerámicos y de Tantalio. OF MULTILAYER CERAMIC AND TANTALUM CAPACITORS (p. 3)

Para la simulación se eligió de estas tablas:

- Capacitor cerámico  $10~\mu F$ , encapsulado 0805, ESL=1050~pH ESR= $600~m\Omega$ .

- Capacitor de tantalio  $10 \ \mu F$ , encapsulado «A», ESL= $2200 \ pH$  ESR= $1600 \ m\Omega$ .

El resultado puede visualizarse en la figura 3.21. Se puede observar del resultado mostra-

| AVX         | Description                        | ESR@100kHz | ESR@1MHz |

|-------------|------------------------------------|------------|----------|

| Part Number |                                    | (mΩ)       | (mΩ)     |

| TAJA105M016 | A case, 1μF, 16V                   | 5000       | 1500     |

| 1206YC105M  | 16V, 1μF, X7R                      | 2200       | 25       |

| TAJA106M010 | A case, 10μF, 10V                  | 1600       | 350      |

| 1206ZG106Z  | 10V, 10μF, Y5V                     | 60რე       | 20       |

| TAJB226M010 | B case, 22μF, 10V                  | 1300       | 1000     |

| 1210ZG226Z  | 10V, 22μF, Y5V                     | 4          | 3        |

| TPSC226M016 | C case, 22µF, 10V<br>low ESR tant. | 300        | 250      |

| 1210ZG226Z  | 10V, 22μF, Y5V                     | 4          | 3        |

Tabla 3.3: Resistencia equivalente en serie de varios capacitores.

Figura 3.21: Alimentación con capacitor de desacoplo Ideal, Tantalio y Cerámico.

Página 41

do que el uso de un capacitor de tantalio o cerámico no desacoplan las corrientes tan bien como uno de ideal, esto era de esperarse. La información de mayor valor se encuentra en comparar los dos capacitores modelados con ESR y ESL, el mejor comportamiento, para un mismo valor de capacidad lo posee el cerámico, que presenta menor ESR y ESL que su contraparte de tantalio. Se espera que independientemente del valor de capacidad, a una determinada frecuencia la respuesta del capacitor es definida por sus características de ESR y ESI y no por su capacidad nominal.

Se verificará la última afirmación comparando el capacitor de tantalio con uno cerámico 100~nF de menor tamaño (encapsulado 0603): C0603C104K8RACTU. Según su hoja de datos presenta un Factor de Disipación o Dissipation Factor (por sus siglás en inglés DF) de  $5\,\%$ , para encontrar la ESR de este capacitor se recurre a la siguiente fórmula (la tabla 3.3 no incluye el valor para este encapsulado).

$$DF = \frac{ESR}{X_c} = 0.05 \tag{3.7}$$

Si se considera una frecuencia de  $f=10\ MHz$ , la reactancia capacitiva  $X_c$  puede ser expresada con la ecuación 3.8.

$$X_c = 2\pi f C = 2\pi (10 \times 10^6)(100^9) = 6.283 \Omega$$

(3.8)

Ahora se calcula la ESR con la ecuación 3.9.

$$ESR = (0.05)(6.283) = 314.16 \, m\Omega$$

(3.9)

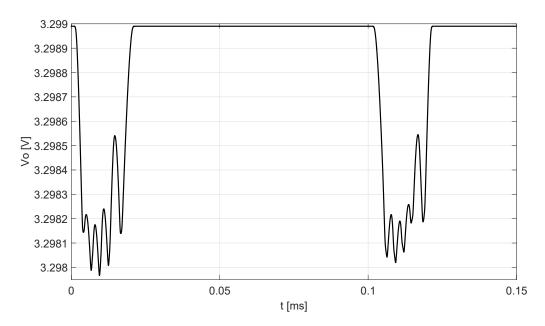

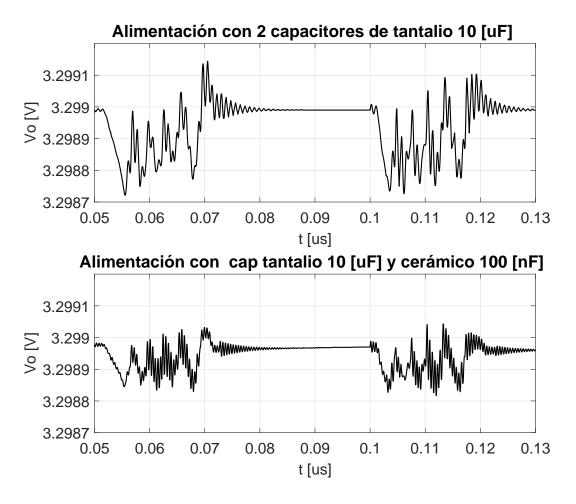

Se realizará una simulación aumentando la frecuencia de las conmutaciones a  $10\ MHz$  y configurando el tiempo de crecimiento a  $10\ ns$ , también se redujeron el número de inversores a 20. La simulación se repetirá en dos configuraciones de desacoplo:

- Desacoplo con dos capacitores de tantalio en paralelo, ambos de  $10~\mu F$  ( $ESR=1.6~\Omega~{\rm y}~ESI=2200~pH$

- Desacoplo con capacitor de tantalio en paralelo a cerámico C0603C104K8RACTU (100~nF,  $ESR = 0.314~\Omega$  y ESI = 850~pH).

Figura 3.22: Simulación con 20 inversores a 10~MHz y tiempo de crecimiento 10~ns.

Como se puede observar en la figura 3.22, pese a que se esperaría menor variación de la alimentación con dos capacitores de tantalio de  $10~\mu F$  (que suman un total de  $20~\mu F$ ), frente a uno  $10~\mu F$  del mismo tipo con uno de 100~n F (que suman un total de  $10.1\mu F$ , sin embargo, el gráfico muestra que para el primer caso la alimentación presenta una variación pico de 0.4~mV mientras que el segundo 0.2~mV. Esto sucede porque a la frecuencia en que se simuló el circuito los capacitores de mayor valor entran en su región inductiva, mientras que el capacitor de menor valor aún sigue en su región capacitiva.

La simulación comprueba que para efectos de usar un capacitor de desacoplo el valor de ESR y ESI que presente importa tanto como el valor de la capacidad misma, también se comprueba la famosa regla de oro o «Rule of thumb» de desacoplar la fuente de alimentación con un capacitor de  $100\ nF$ . Esta regla comprobada se visualizará en el uso de capacitores de  $100\ nF$  en encapsulado 0805, los cuales se escogieron sobre la versión de encapsulado 0603 considerando no solo la capacidad de desacoplo, sino que también la facilidad de soldado en el PCB final y disponibilidad en el mercado (descartando importaciones).

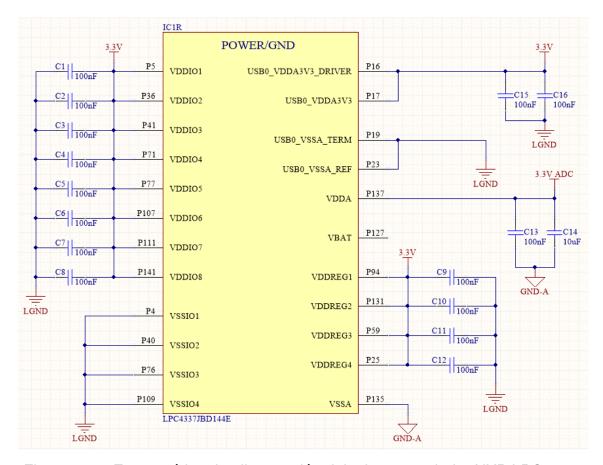

La directa aplicación de este regla sobre el diseño realizado se puede observar en la figura 3.23. En la figura 3.23 se puede apreciar en un solo bloque todos los pines de